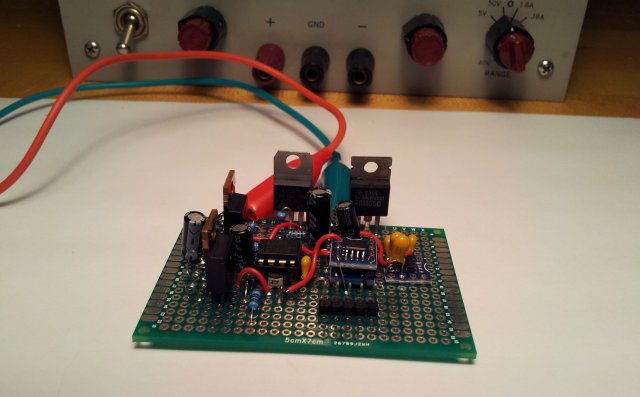

Recently, some pretune DAC and microcontroller circuitry has been build, see earlier post. This is now basically functional, however, we need to confirm that is is really working as desired. Never trust any circuits just build – especially when it comes to “unpredictable” aspects like noise. The parts used, they will most likely perform up to their specification, but there can be all kinds of hidden issues that will later on lead to lengthy troubleshooting of phase noise or spur issues.

From experience, power supply related noise is one of the most severe and troublesome item, if not taken care of at an early stage of design, or prototype construction.

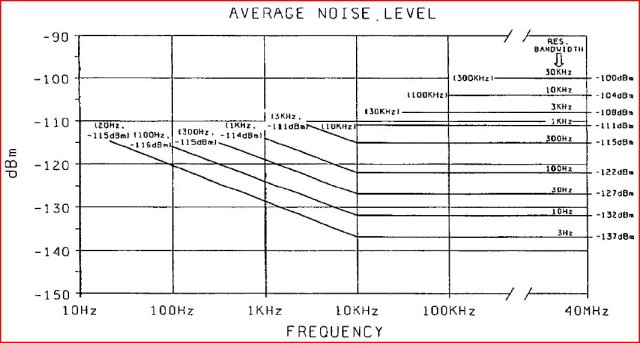

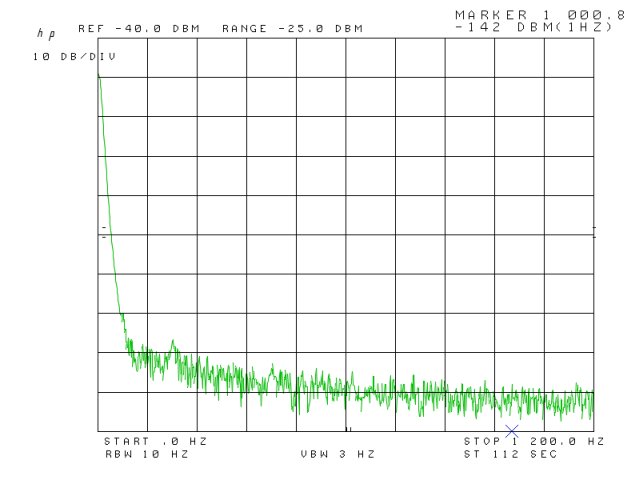

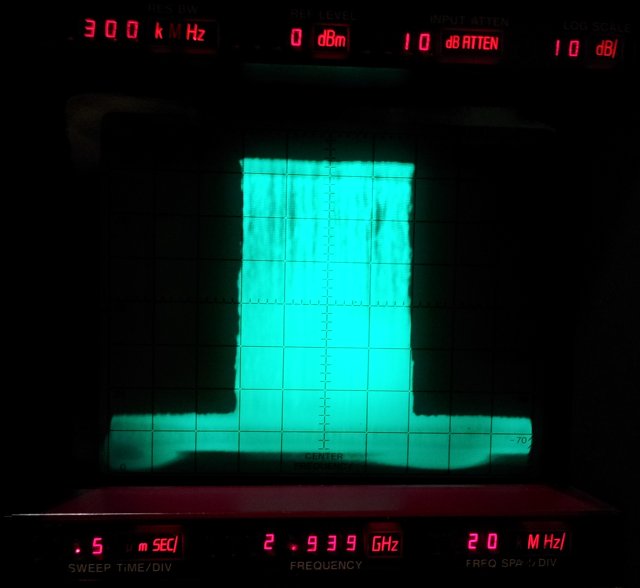

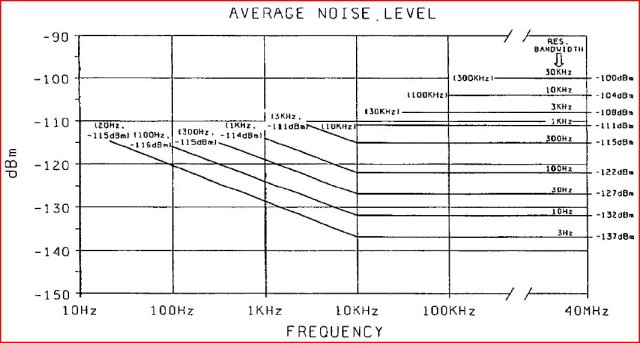

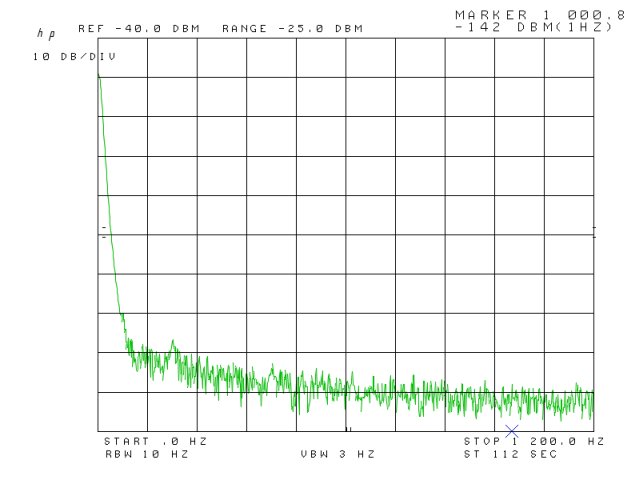

Many articles exist on how to characterize power supply noise, especially at very low levels. This is not really what we need here, because we are talking about a real-world circuit that will later work with a mains power supply, in a reasonably well shielded case. So, our standard will be the lowest noise analyzer I have around here, an HPAK (HP Agilent, now: Keysight) 3585A Spectrum analyzer. This has pretty low noise anyway, down to -137 dBm for a 3 Hz bandwidth.

The only downside of the 3585A, it is about 80 pounds – you will need a sturdy bench and a strong assistant to lift it.

As a side note: The instrument on my bench, it has an interesting sticker, formerly owned by ST (STMicroelectronics, formerly known as SGS-Thomson as printed on the cal label). ST does a pretty massive amount of R&D in the field of semiconductors, and has a long-standing history of inventions. Well, fair enough, I got this instrument in bad shape, seems to have passed through many hands since ST time, but it is now fully repaired and calibrated, providing great service.

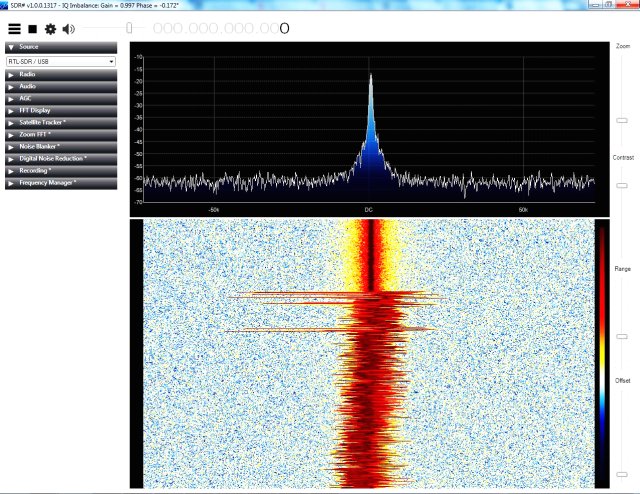

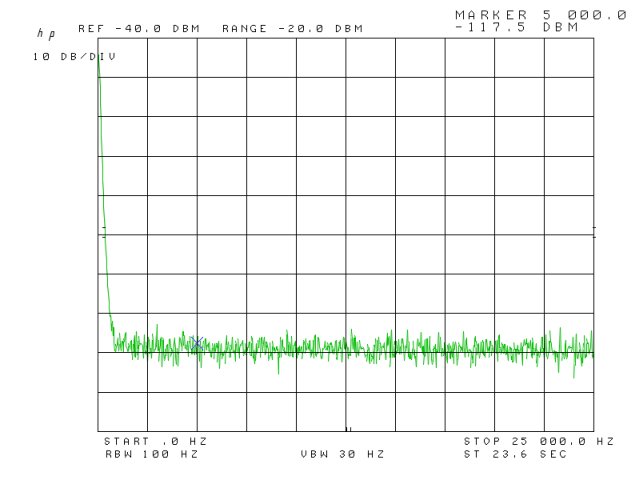

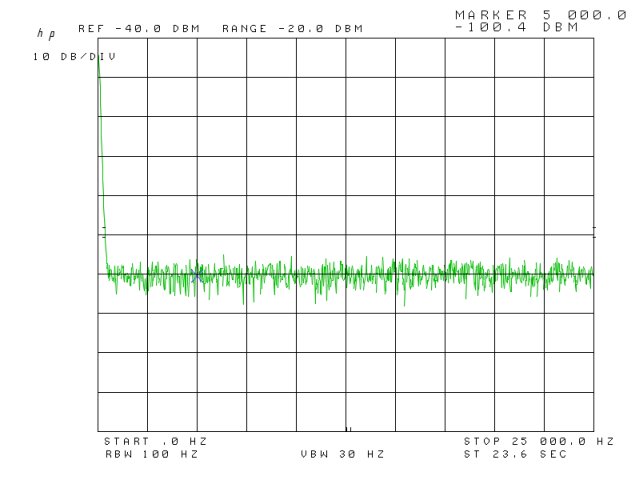

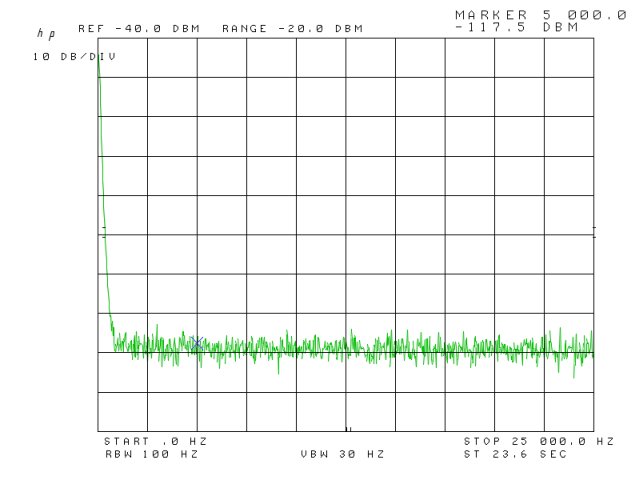

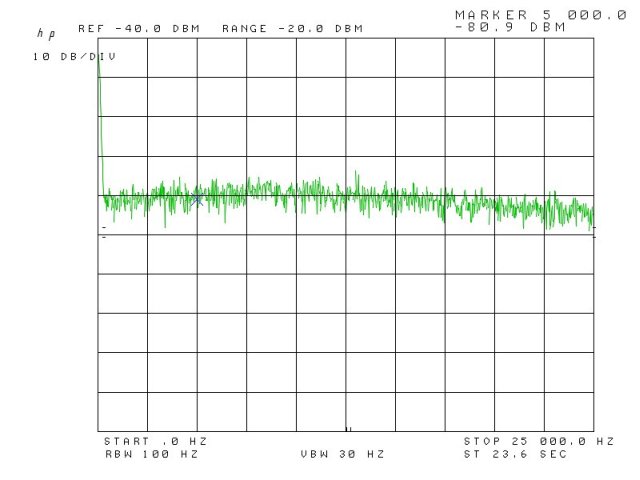

Step (1) – analysis of the circuits already build. Just some 0-25 kHz spectra.

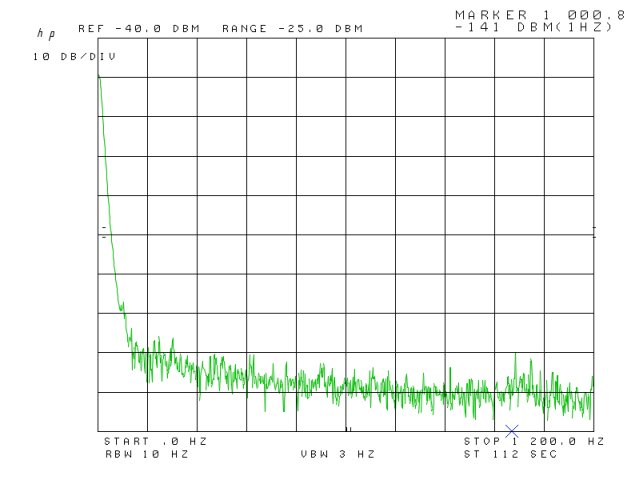

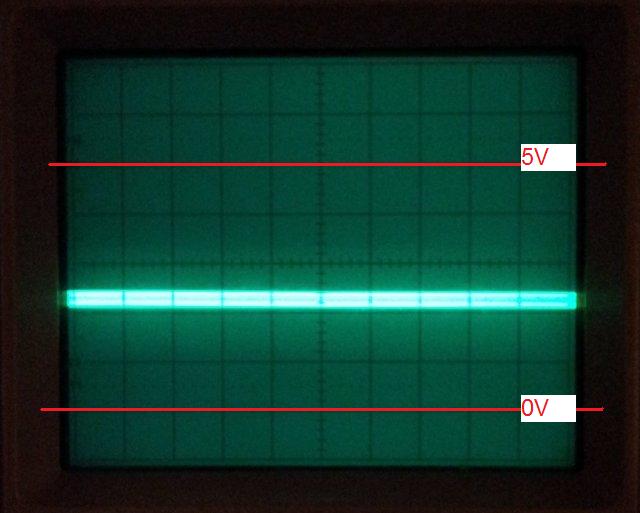

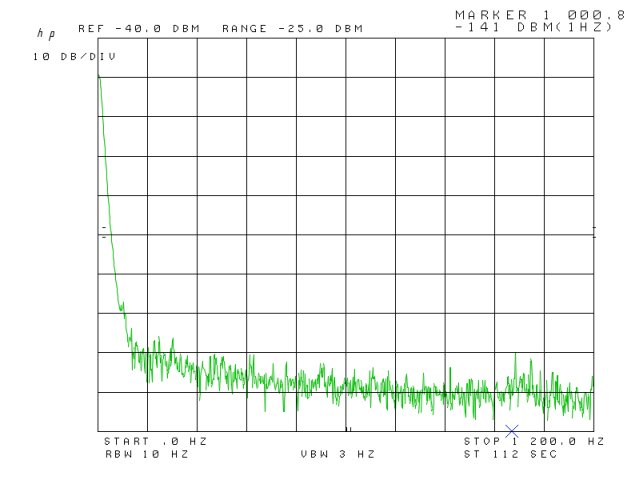

Noise floor, probe grounded at AGND.

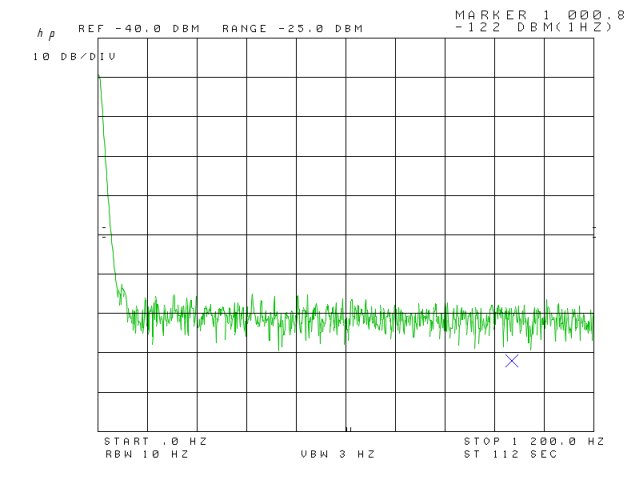

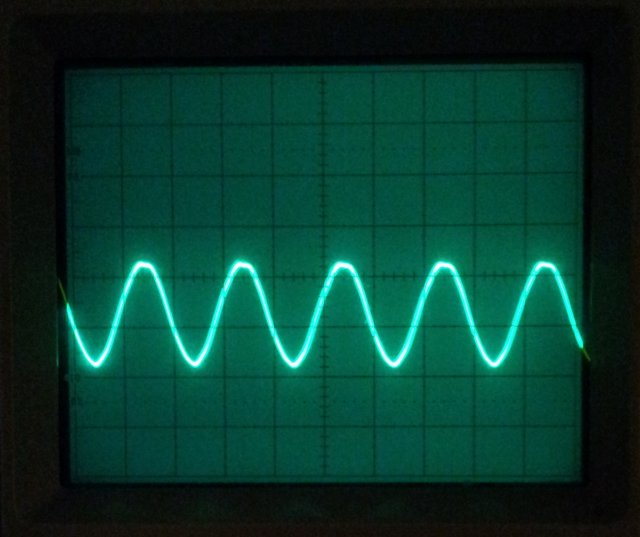

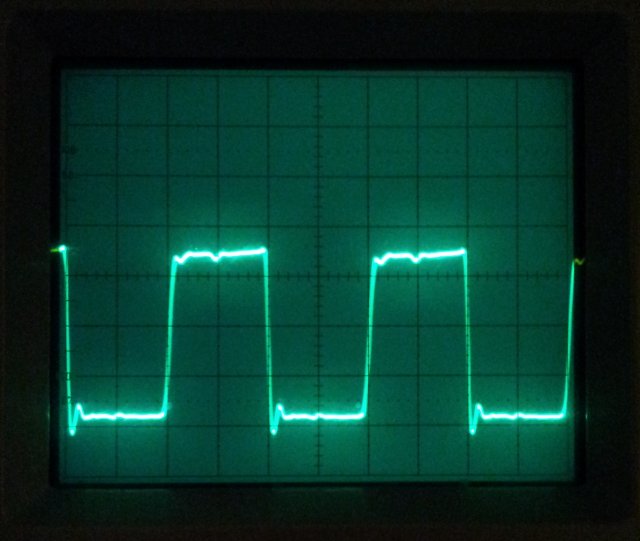

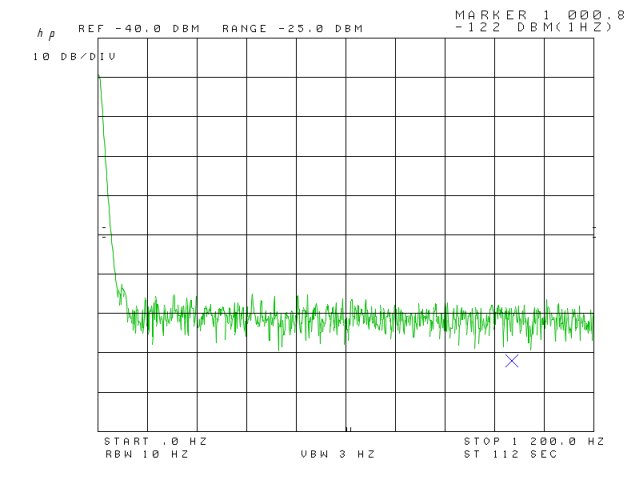

317 regulator output (11.4 V)

– well, much worse than expected! More than 30 dB above the noise level!!

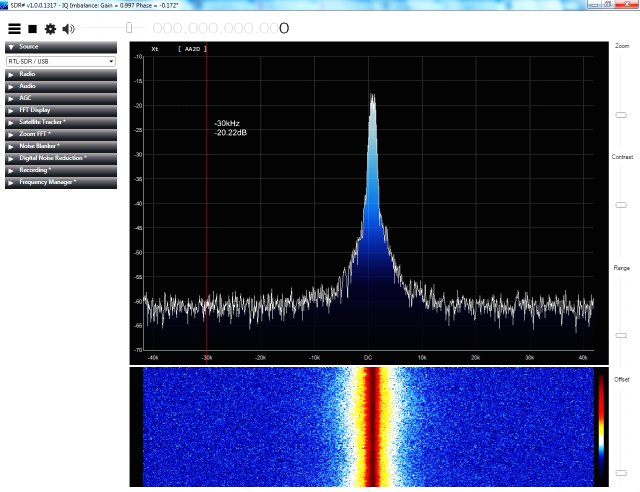

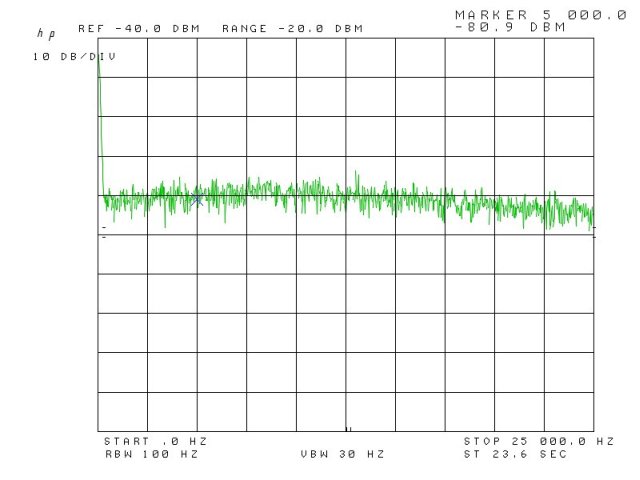

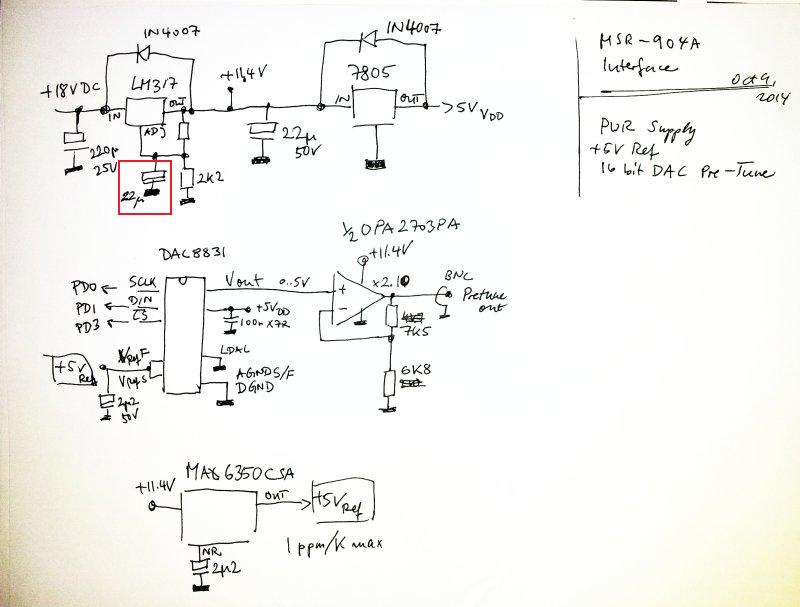

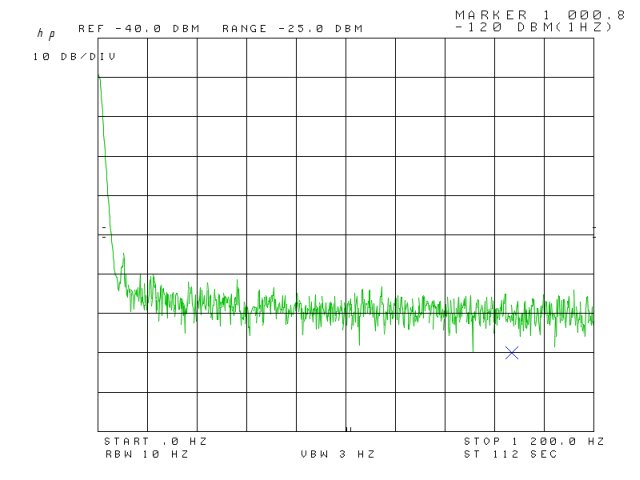

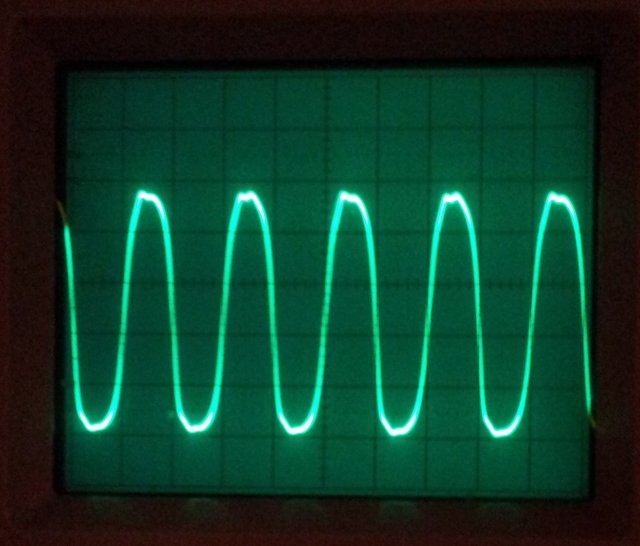

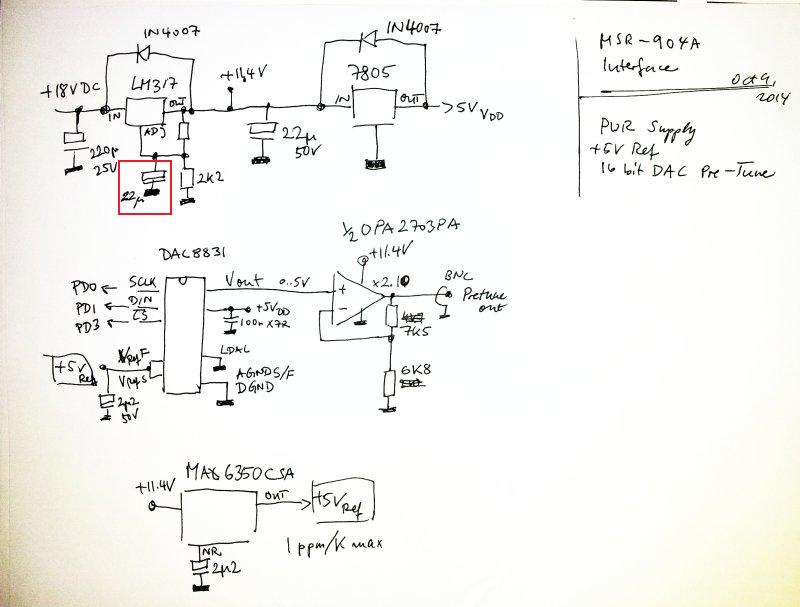

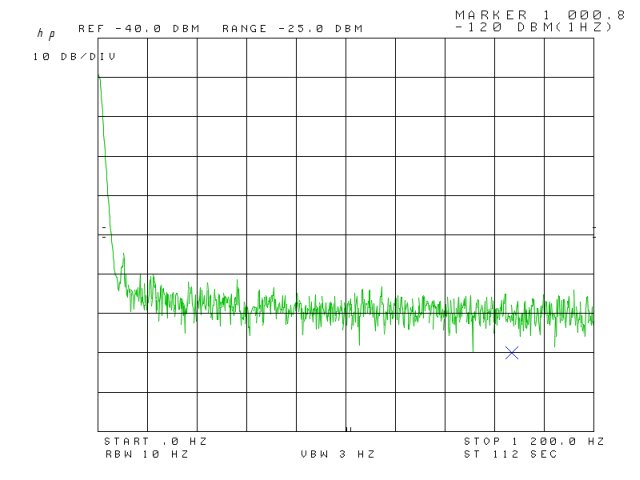

Well, after scratching my head for a while – and doing some measurements around the not-too-complicated 317 circuit, one 22 uF cap was added, to the adjustment input. Ideally, for best frequency response, use a low ESR cap, with wide response, like a tantalum or multilayer ceramic. I could not be bothered, just used a plain electrolytic.

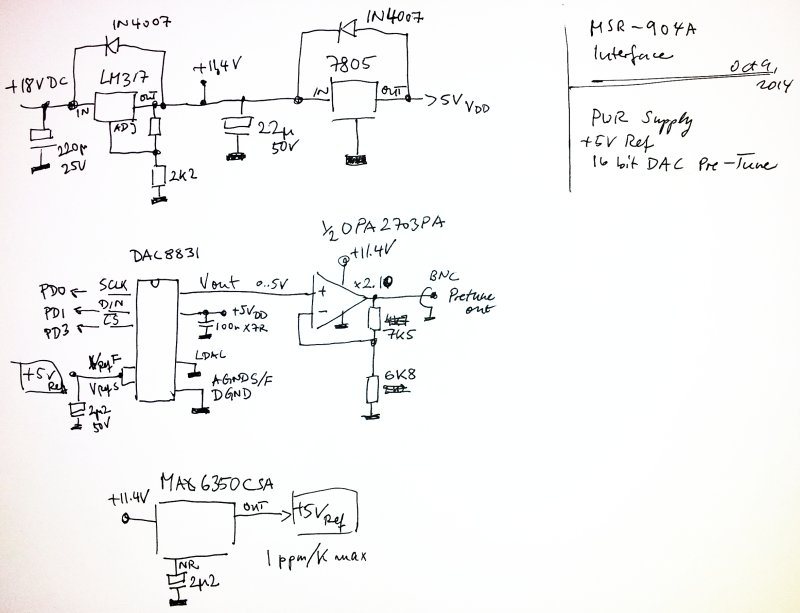

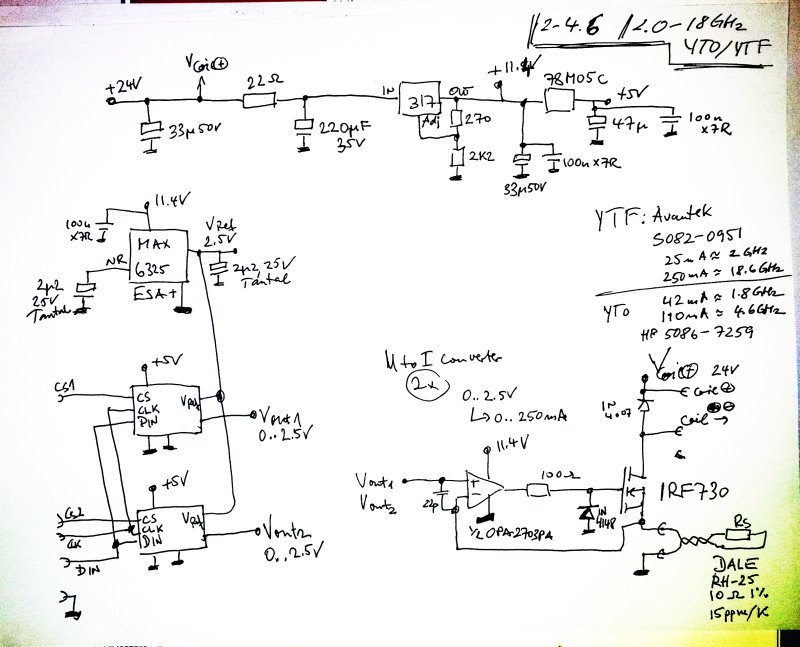

Improved schematic:

(red frame shows additional cap)

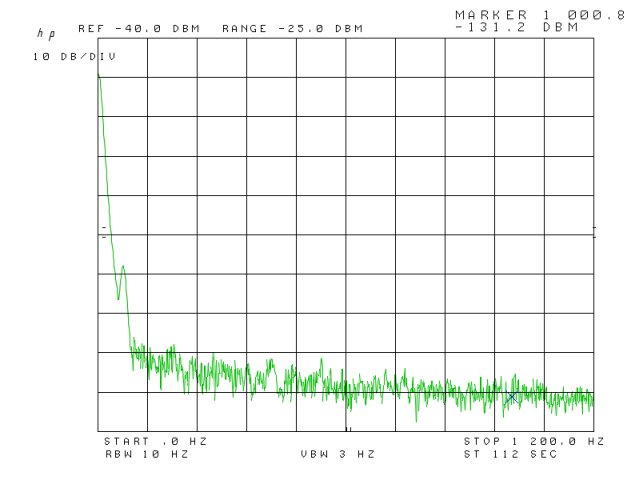

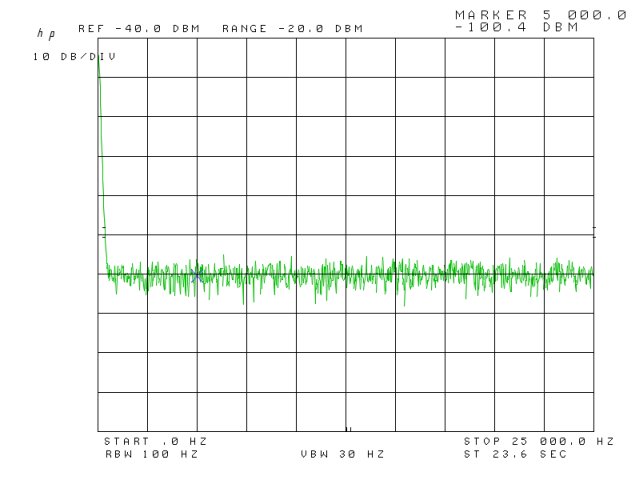

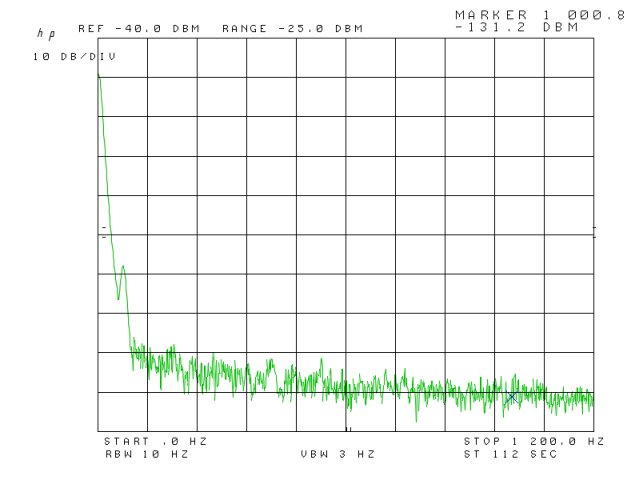

The result:

A 20 dB improvement, fair enough!

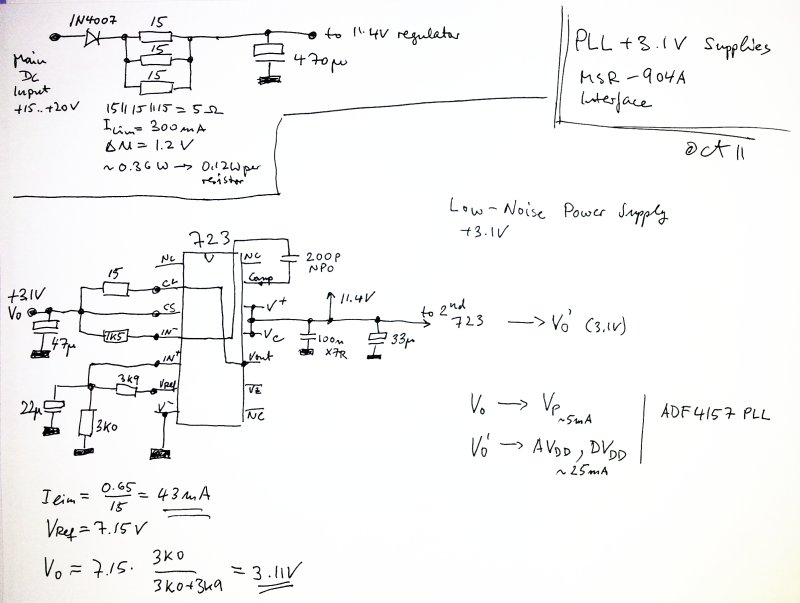

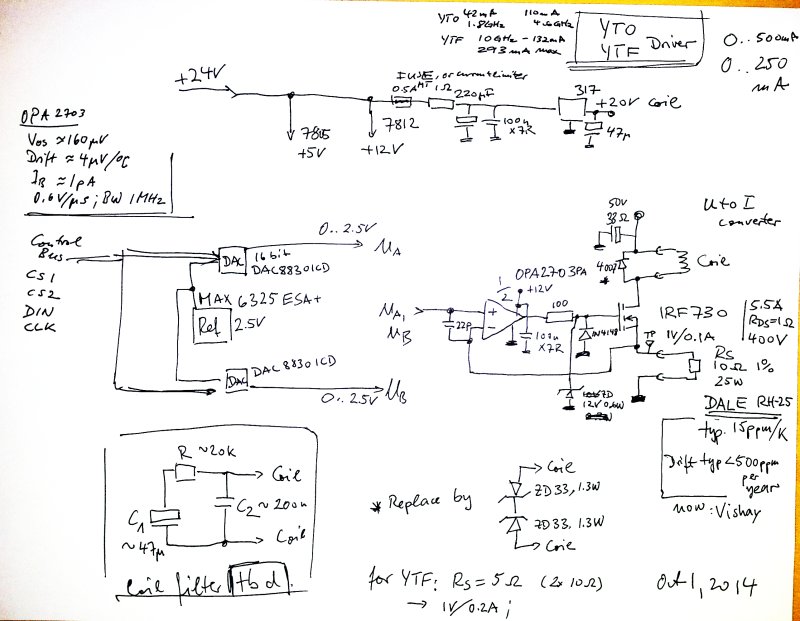

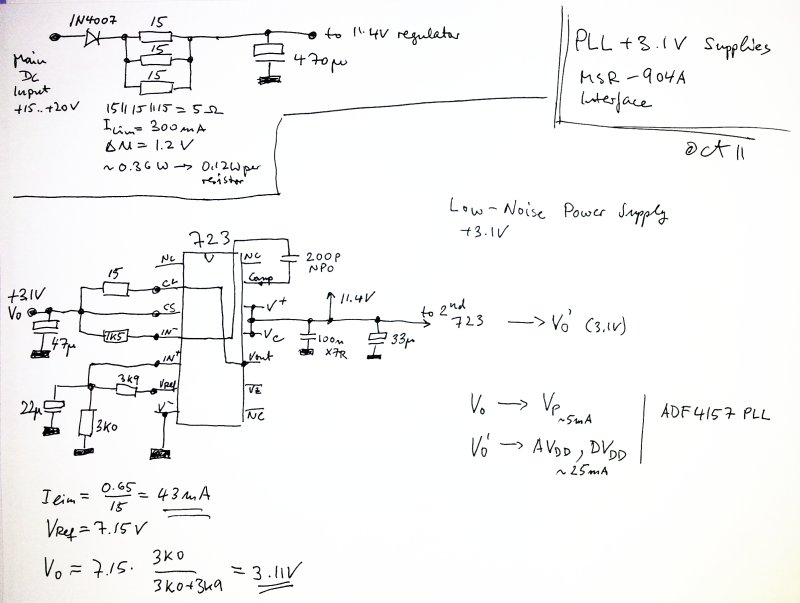

Step (2) – PLL low noise power supplies (2x 3.1 V)

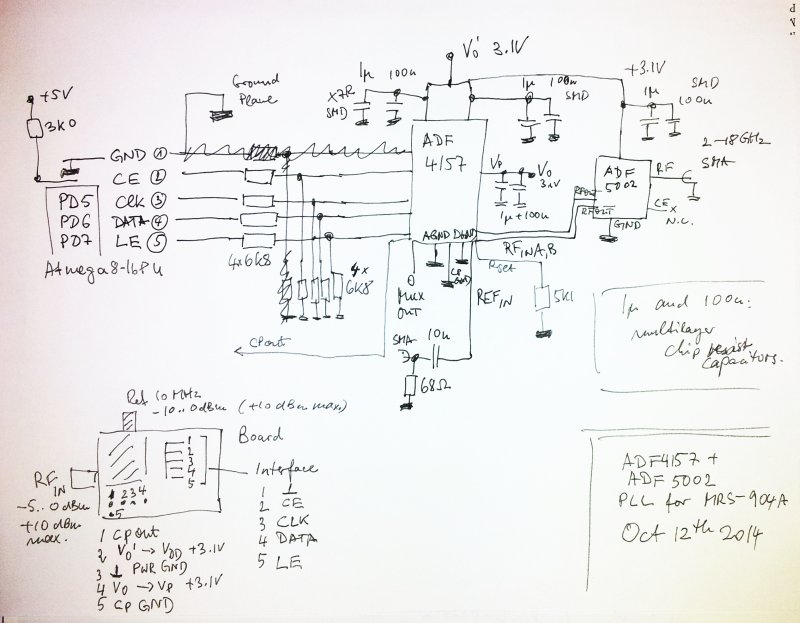

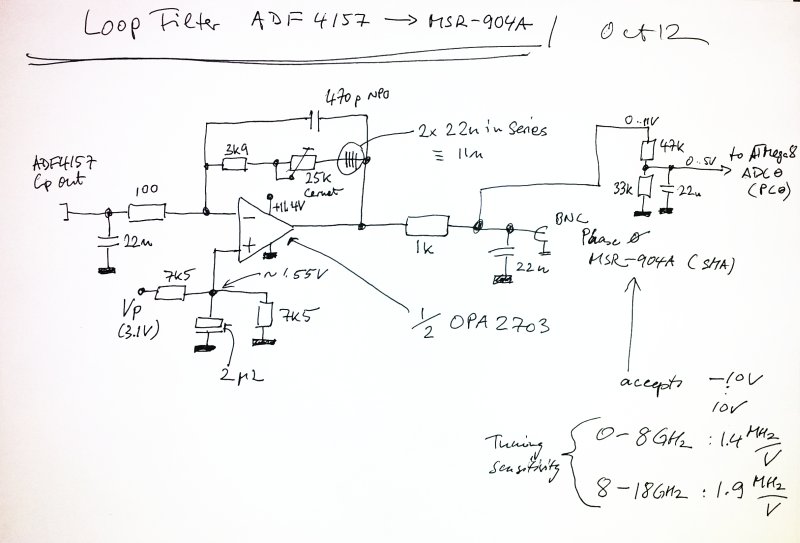

The PLL (an ADF4157 fractional-N synthesizer with ADF5002 prescaler) requires a +3.1 V power supply (2.7 to 3.3 V for the ADF4157, 3.0 to 3.6 for the ADF5002 – so I decided on 3.1 V for both devices). Also, we need a charge pump supply, for the ADF4157. This can be up to 5.5 V, but for simplicity of design, and to follow earlier (rather commercial) designs I did fully using 3.3 V technology, another independent supply is required, for 3.1 V.

These supplies need to very low noise, supply line noise will end up at the charge pump output, increasing phase noise. Glitches on the PLL supply lines can cause all kinds of issues, even the reliability of the circuit might be compromised (miscounting of the prescaler, etc.).

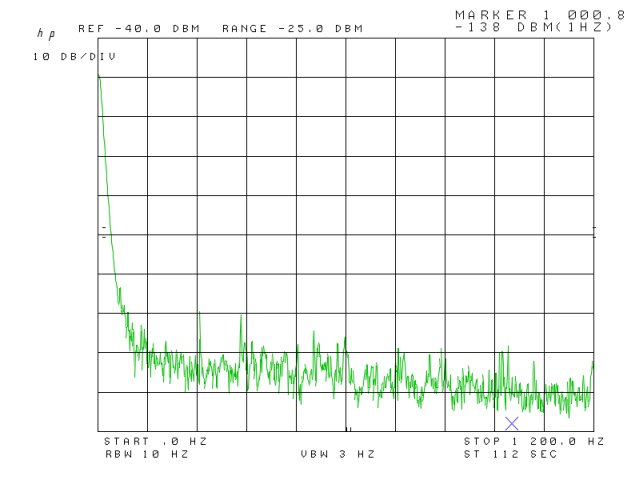

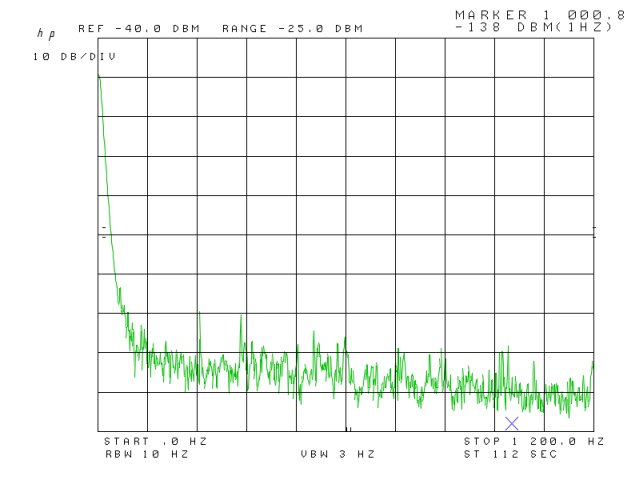

Quite a few more recent parts exist to provide about 3 V regulated output (see TI, Analog, LT), but these devices are non too widespread, and not much better, if not even worse than a trusty old part: the LM723 (aka µA723) regulator. This has a low noise reference build in, and should provide much better performance than any 3-pin regulator.

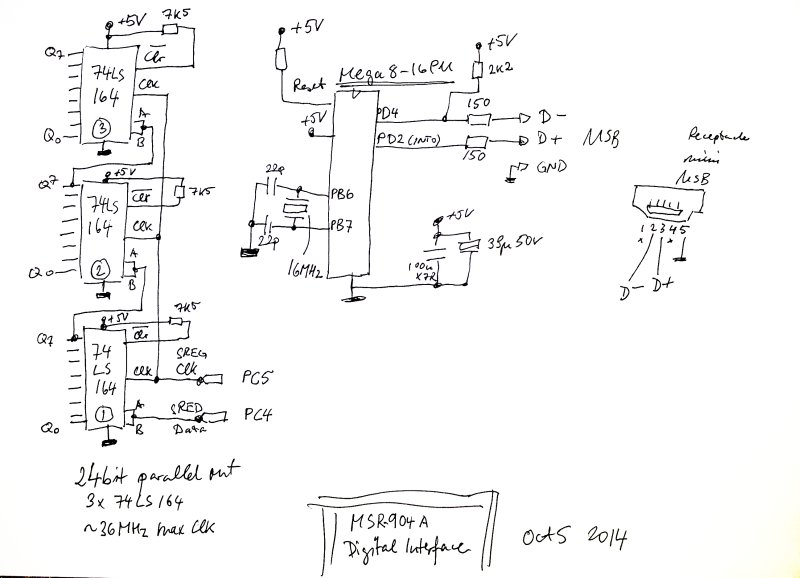

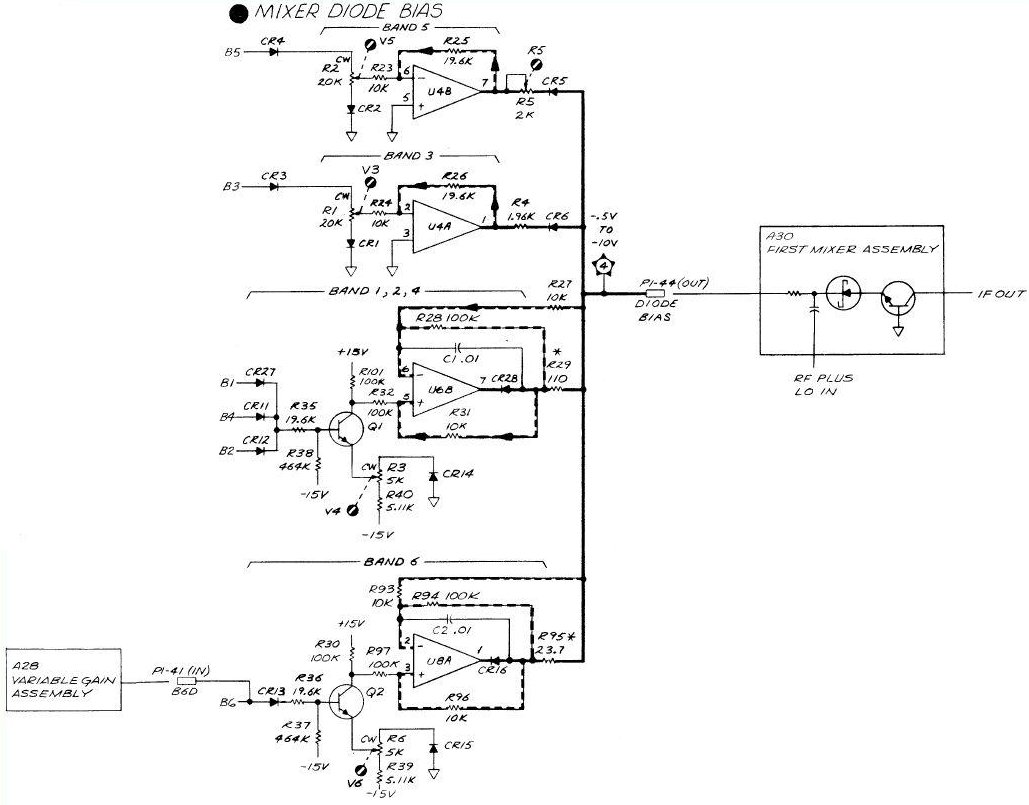

The schematic – main DC input, and 3.1 V low noise power supply section:

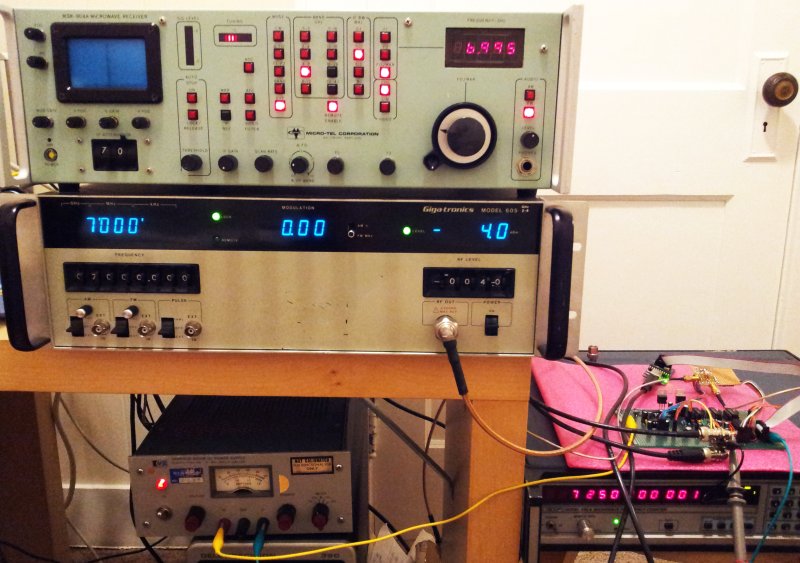

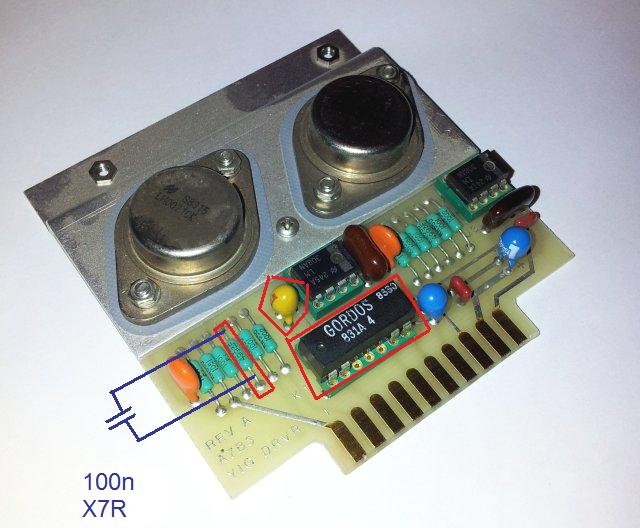

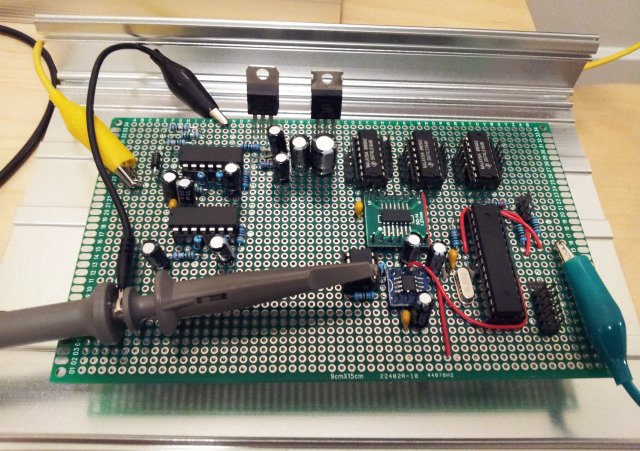

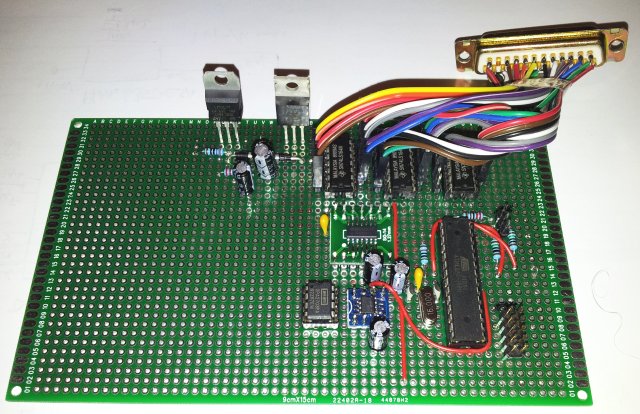

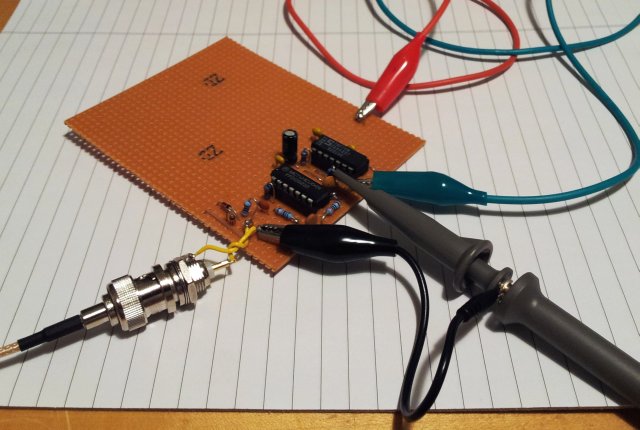

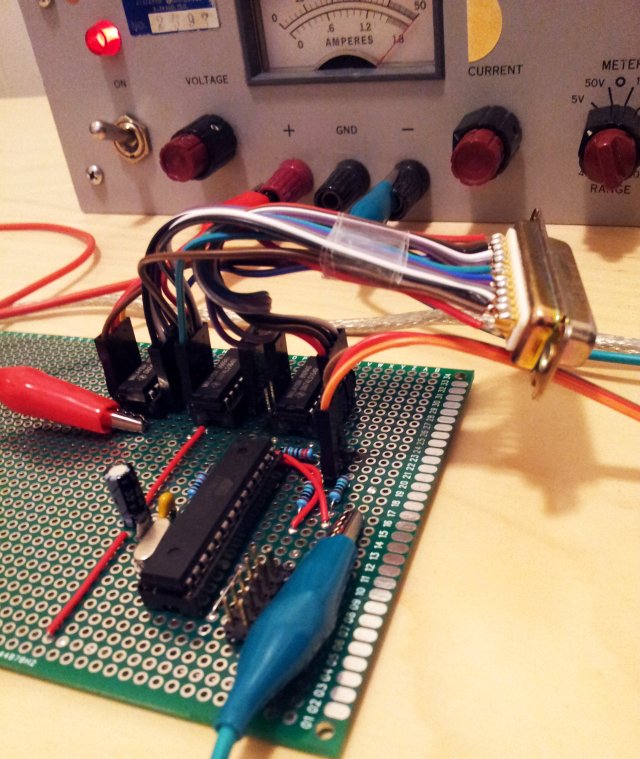

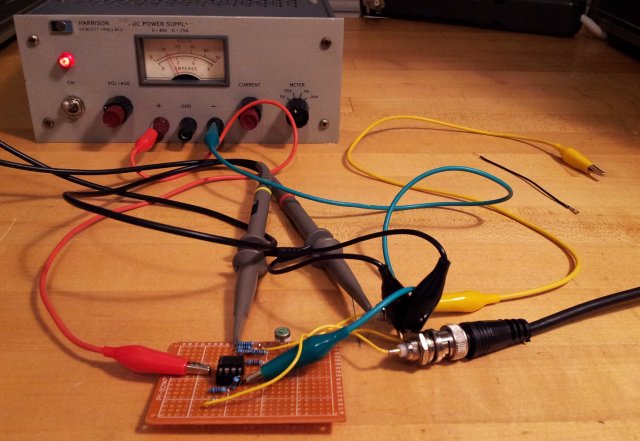

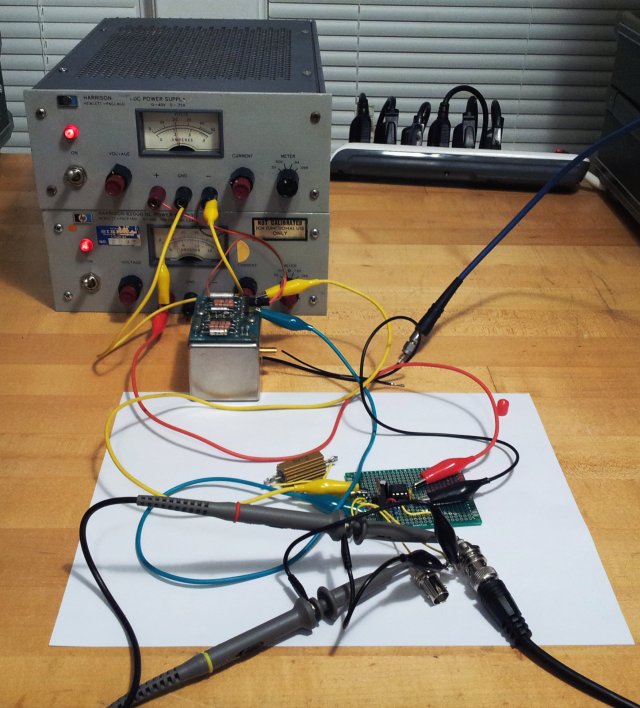

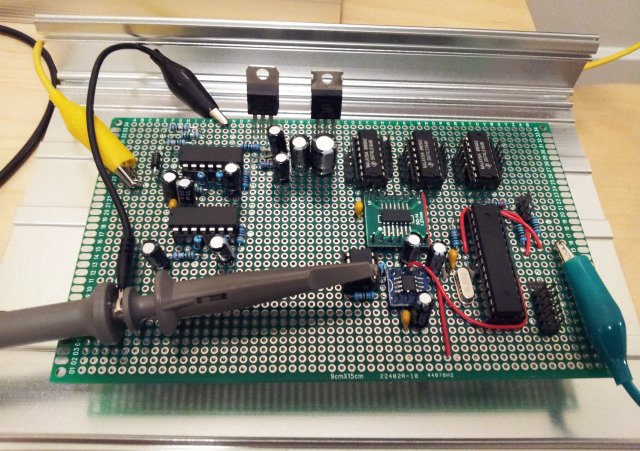

That’t the little board, during test:

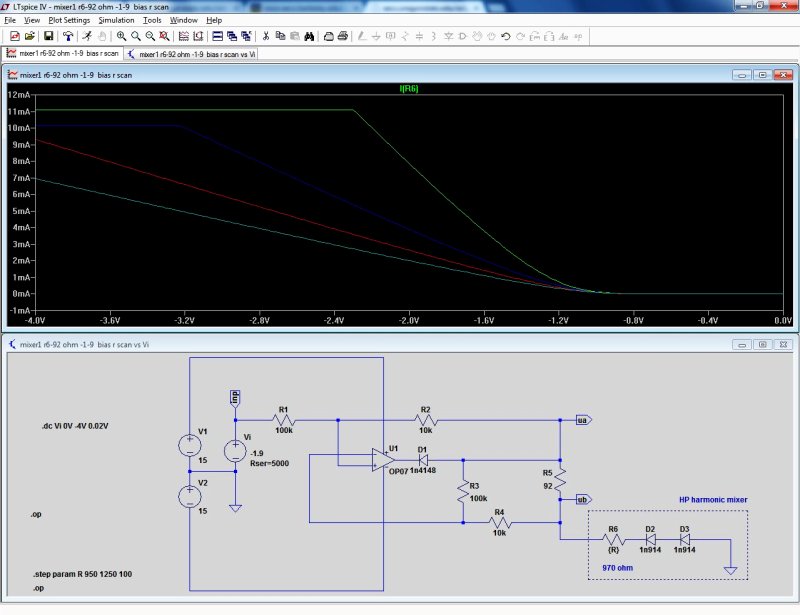

And here, we have the results – all tests now using 1.2 KHz stop frequency (not much going on at higher frequencies), 10 Hz resolution bandwidth, 3 Hz video bandwidth, and, using the noise measurement function of the 3585A – this directly measures and calculates the noise level, at a given frequency, for a 1 Hz bandwidth. Very handy for conversion to nV/sqrt-Hz (nV divided by square-root Hertz is a common way of expressing power supply noise).

Noise floor:

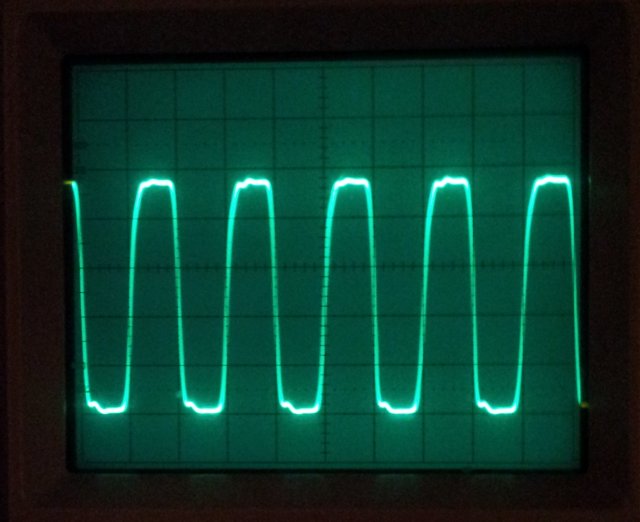

The 317 output (11.4 V) – supply of the pretune DAC circuit and amplifiers, and for the PLL active loop filter

The 7805 output (5 V) – digital supply, DAC supply

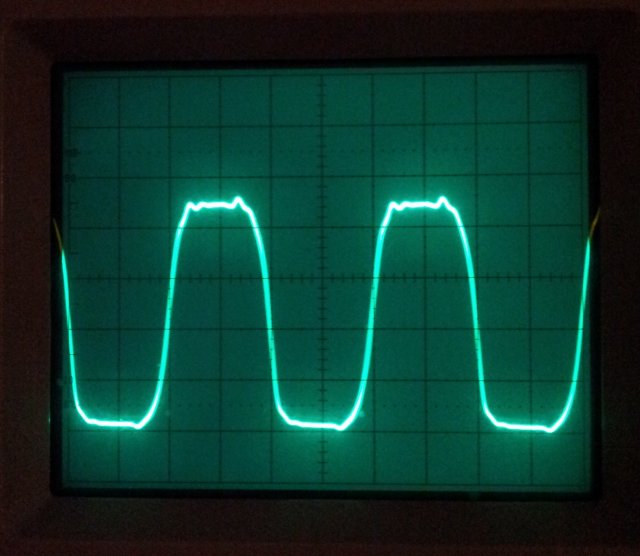

The 723 output (3.1 V) – Vdd section

The 723 output (3.1 V) – Vp section (charge pump supply)

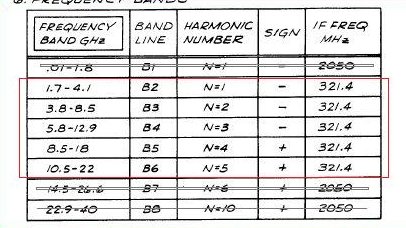

A converter worksheet, to relate the dBm numbers, to nV/sqrt-Hz (calculation also has provisions to convert from other bandwidth – not considering a few extra dB to account for the averaging nature of the detector, etc. – we rely on the 1 Hz normalized value of the 3585A anyway, just in case you need to convert from other BW, please keep dectector response related offset correction, if the task requires such levels of accuracy).

power supply noise calc 3585a

Converted values

-141 dBm – about 20 nV/sqrt-Hz (Vp supply) – very close to noise floor of the setup, the LM723 still seems good enough!

-122 dBm – about 180 nV/sqrt-Hz (5 V, 11.4 V supply)

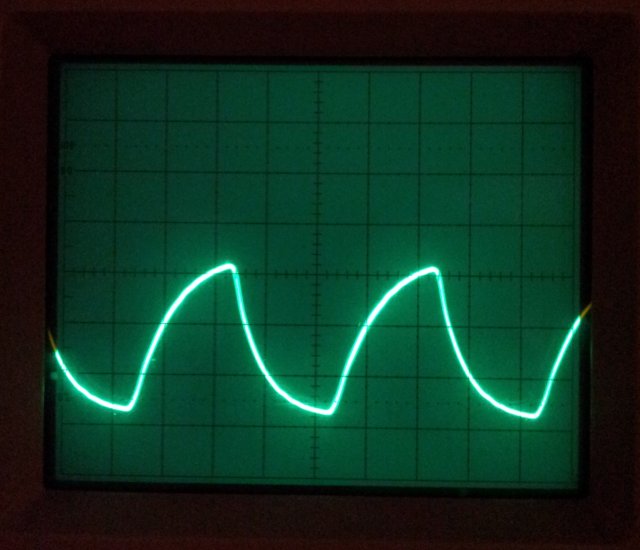

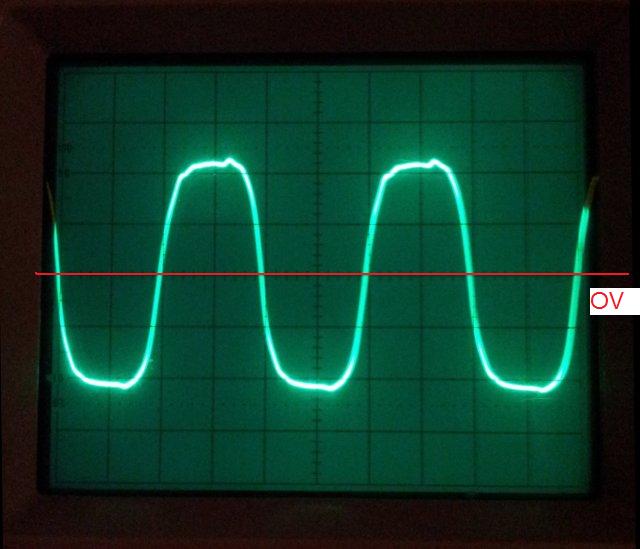

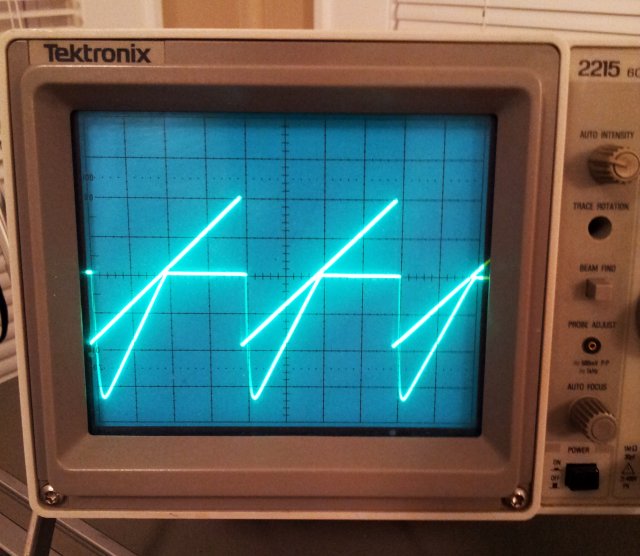

Also, quick look at the DAC pretune output – at the OPA2703 scaling amplifier output:

Virtually, below noise floor.

Note: there are some litte contributions at 60 Hz/180 Hz from mains. These are due to the test setup/signals picked-up by the test cables – don’t seem to originate from the circuit itself.