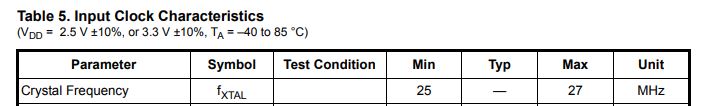

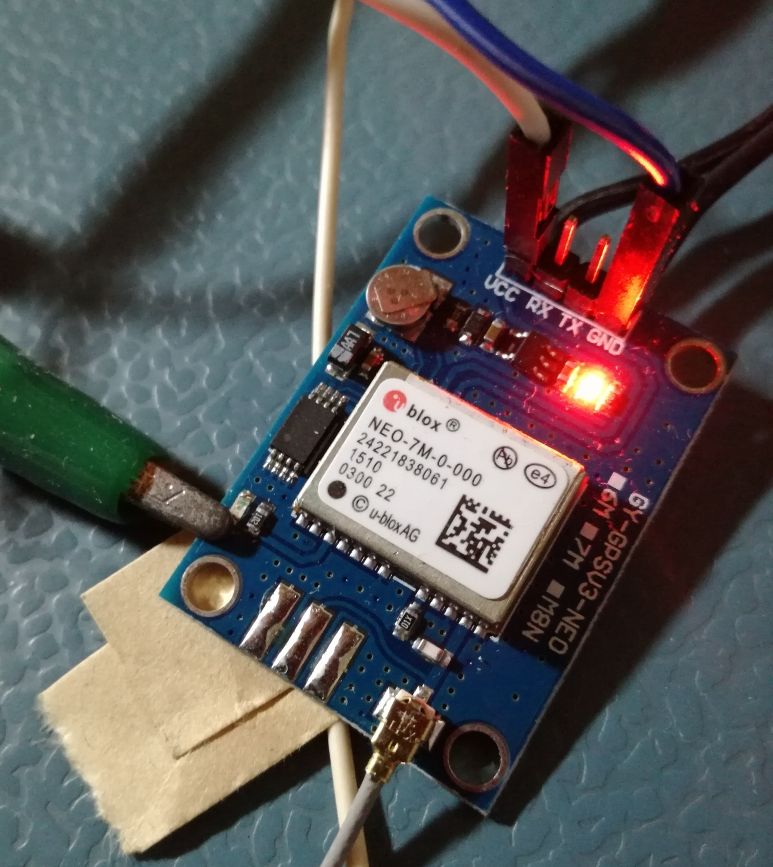

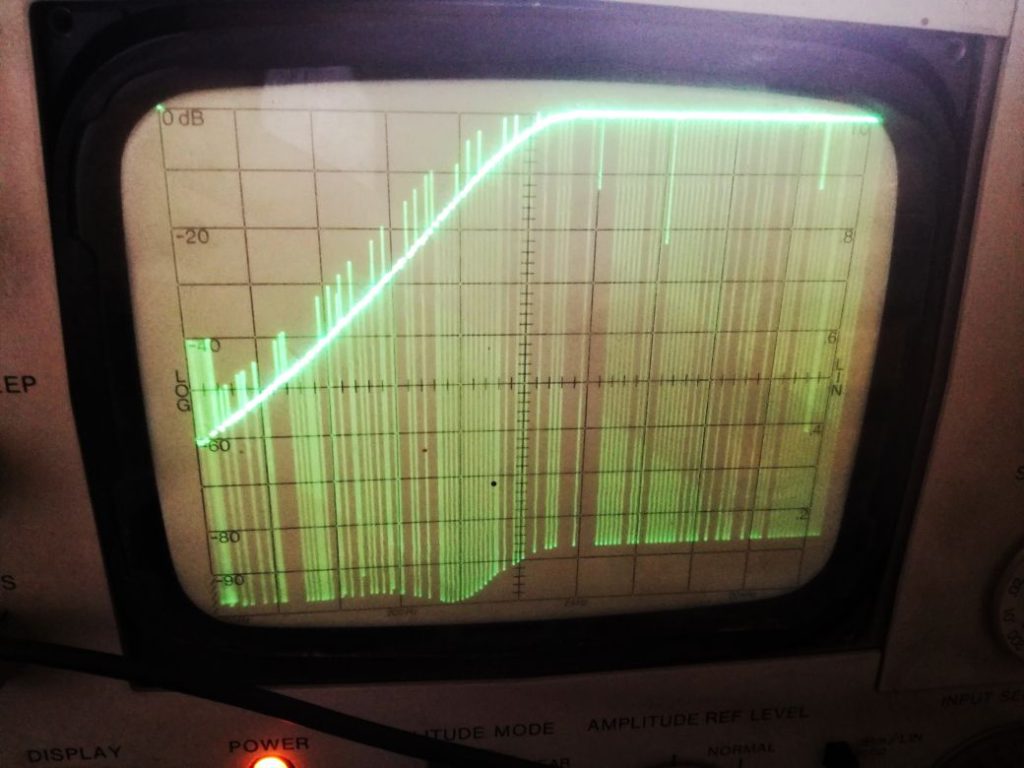

With the Si5351A mastered, time for some tests with the actual application, the GPS receiver (and later GPSDO system).

Two tests were performed:

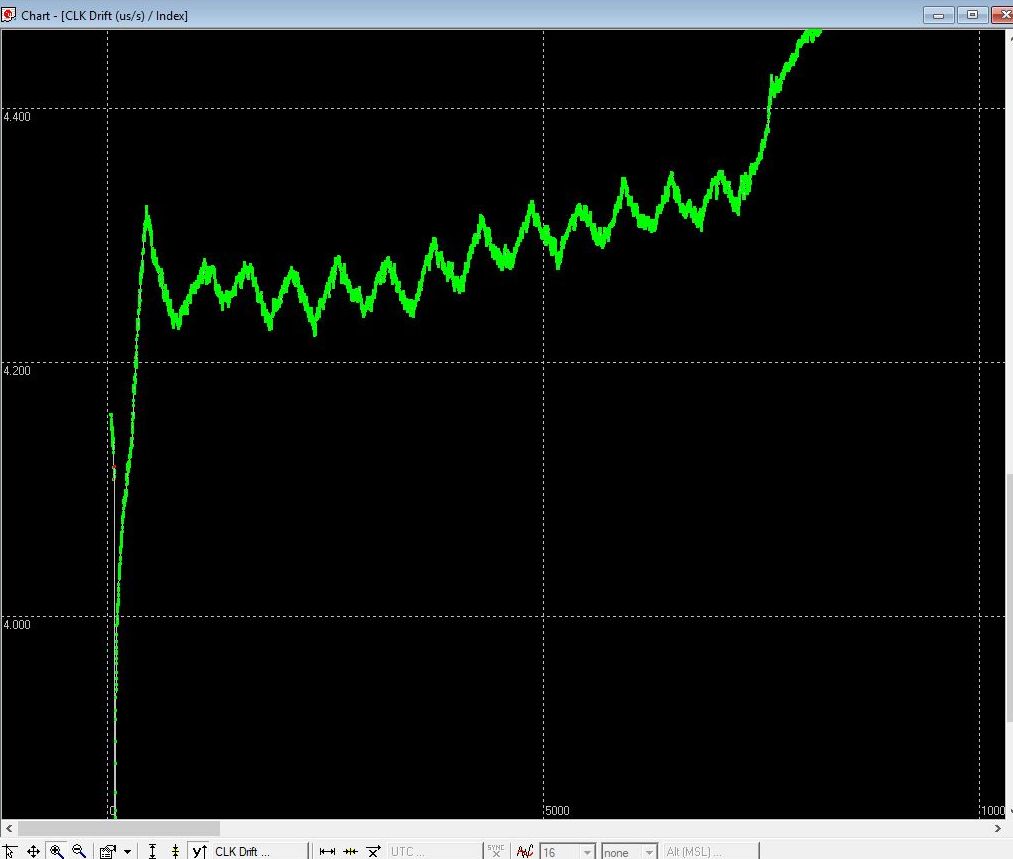

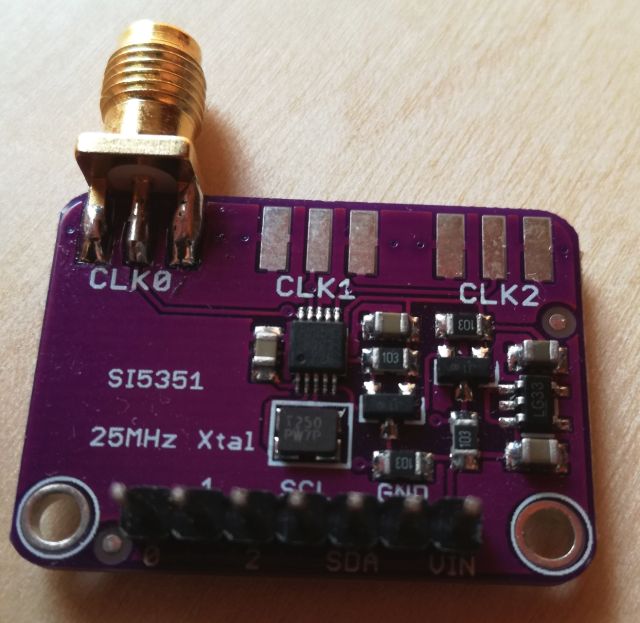

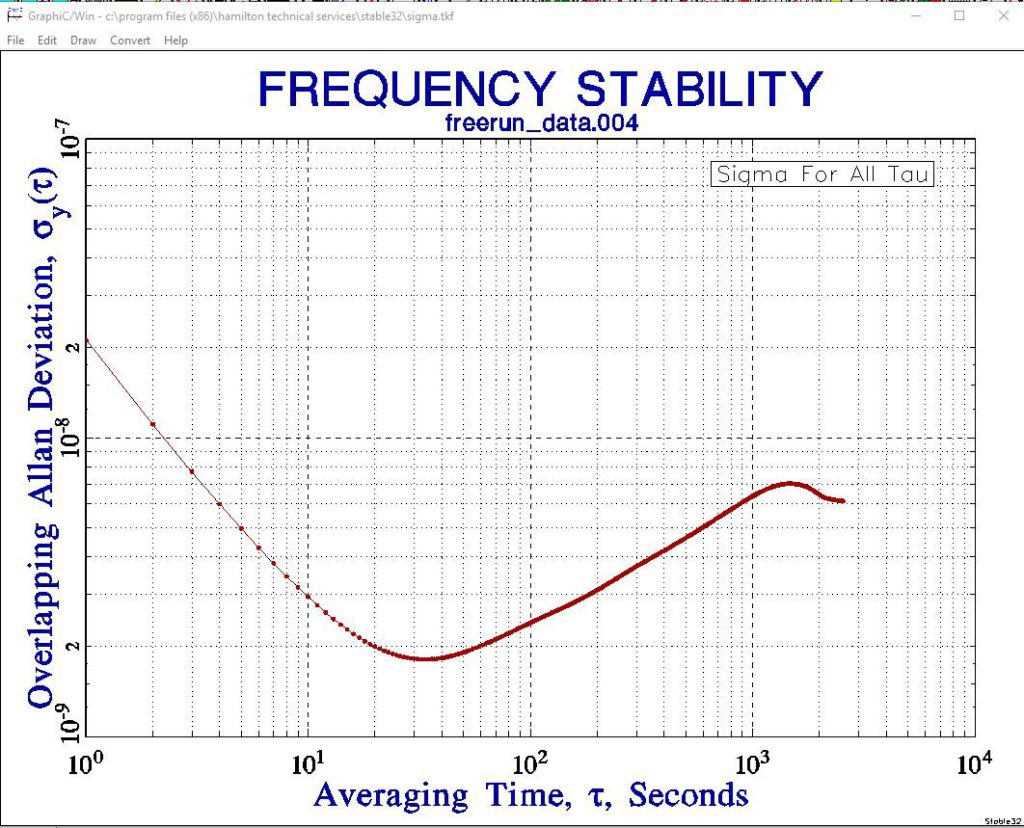

(1) Using the Si5351A clock generator with a standard, not specifically selected or particularly stable crystal. Presumably, an AT cut crystal, running at 25 MHz.

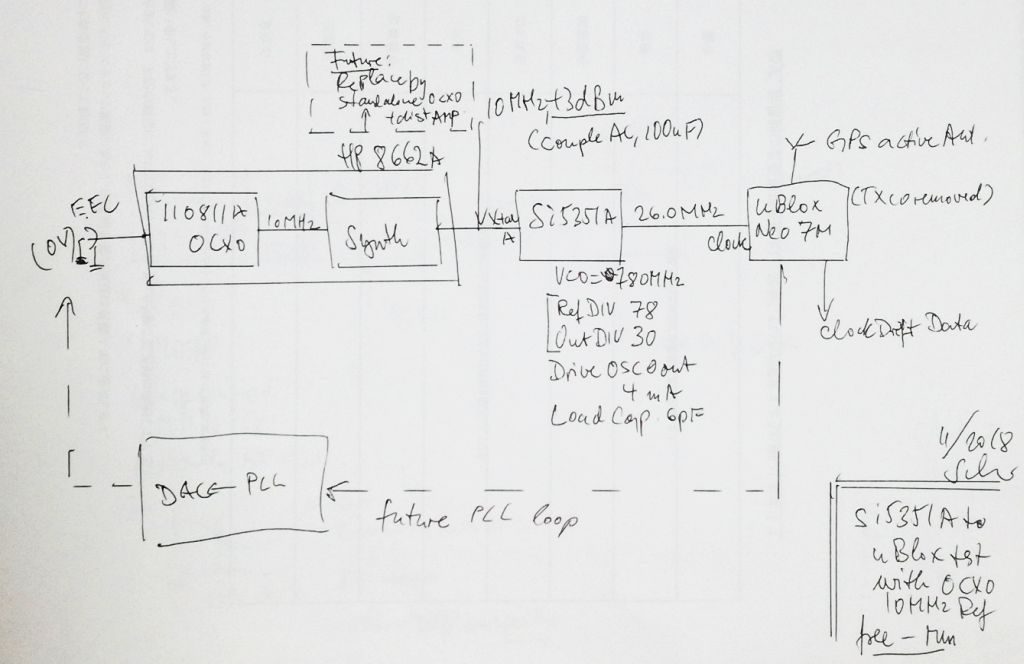

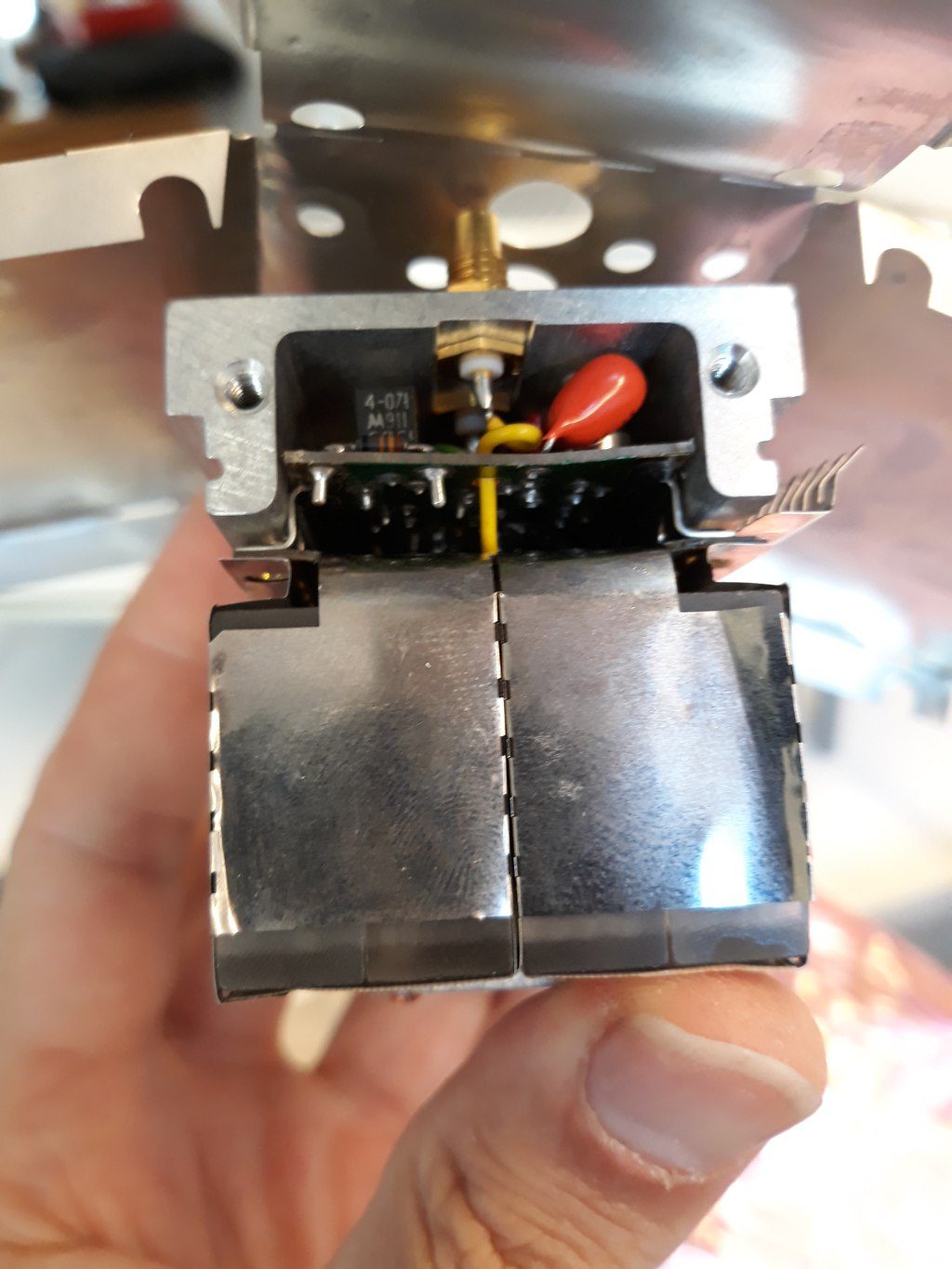

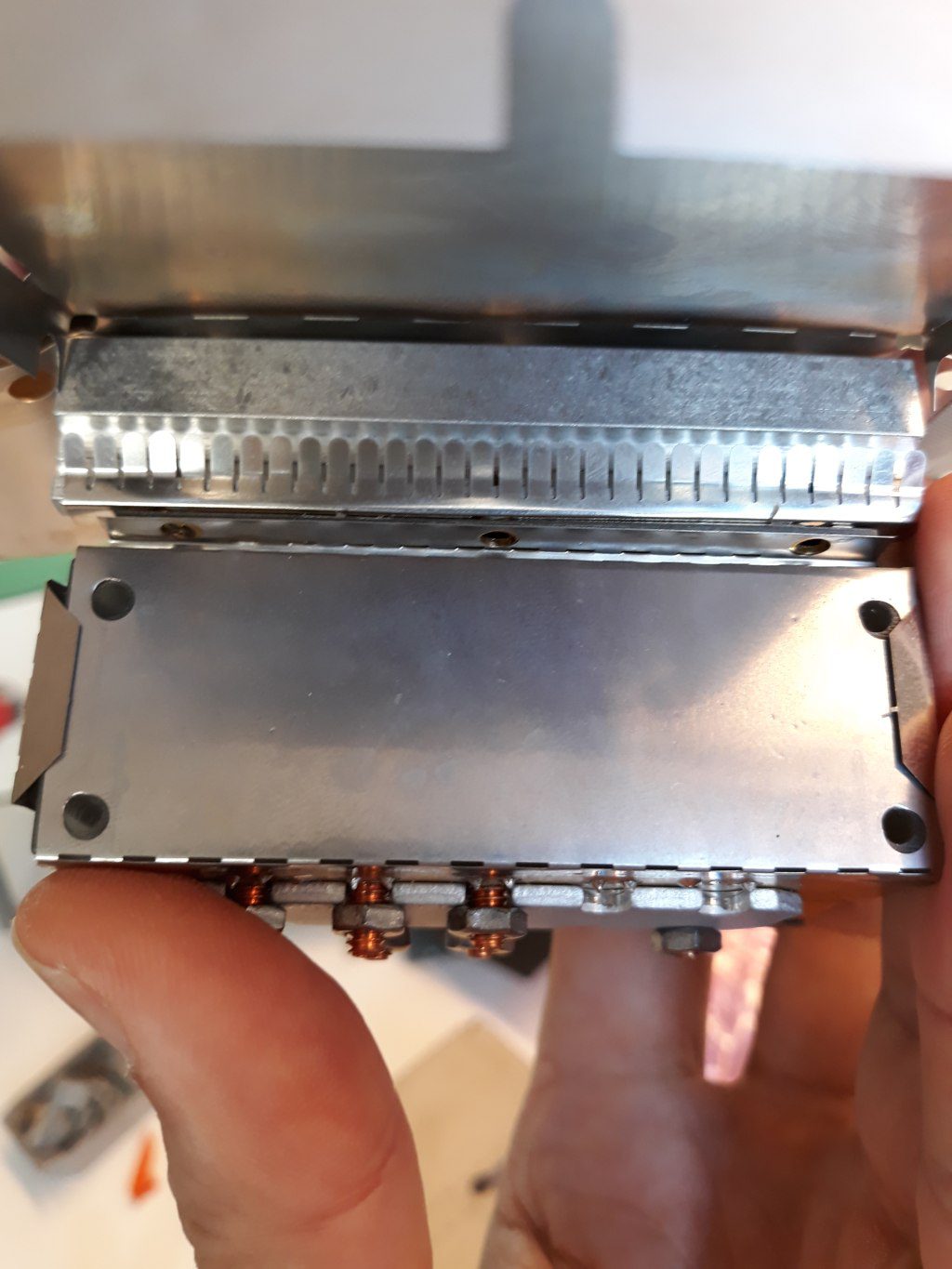

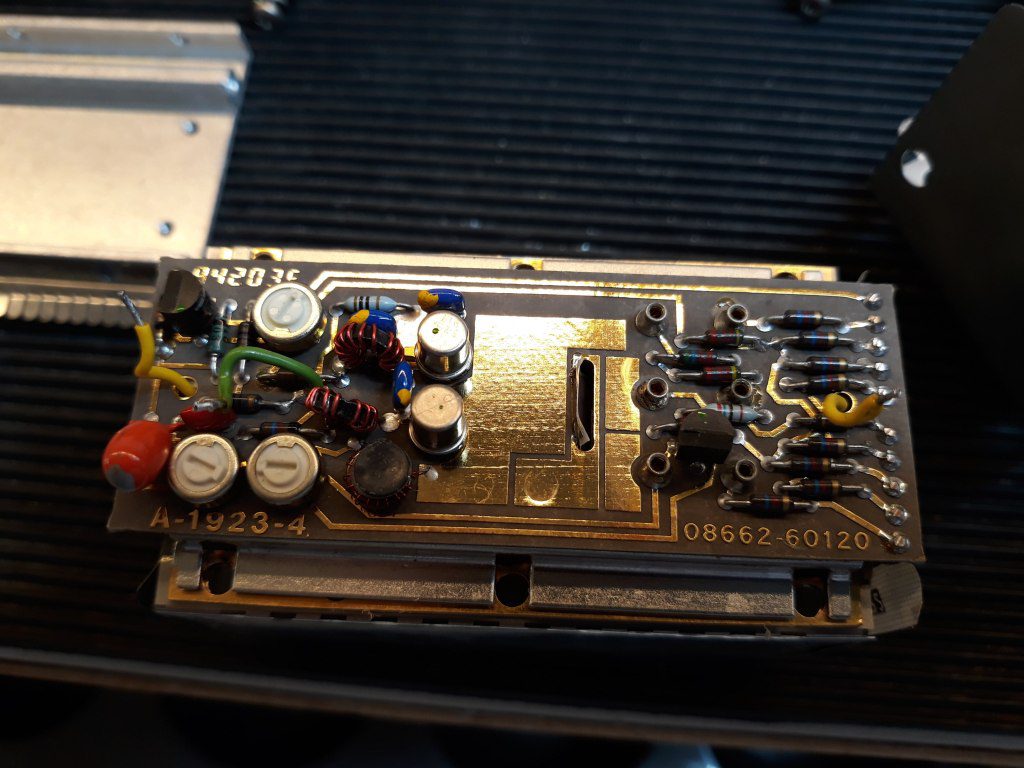

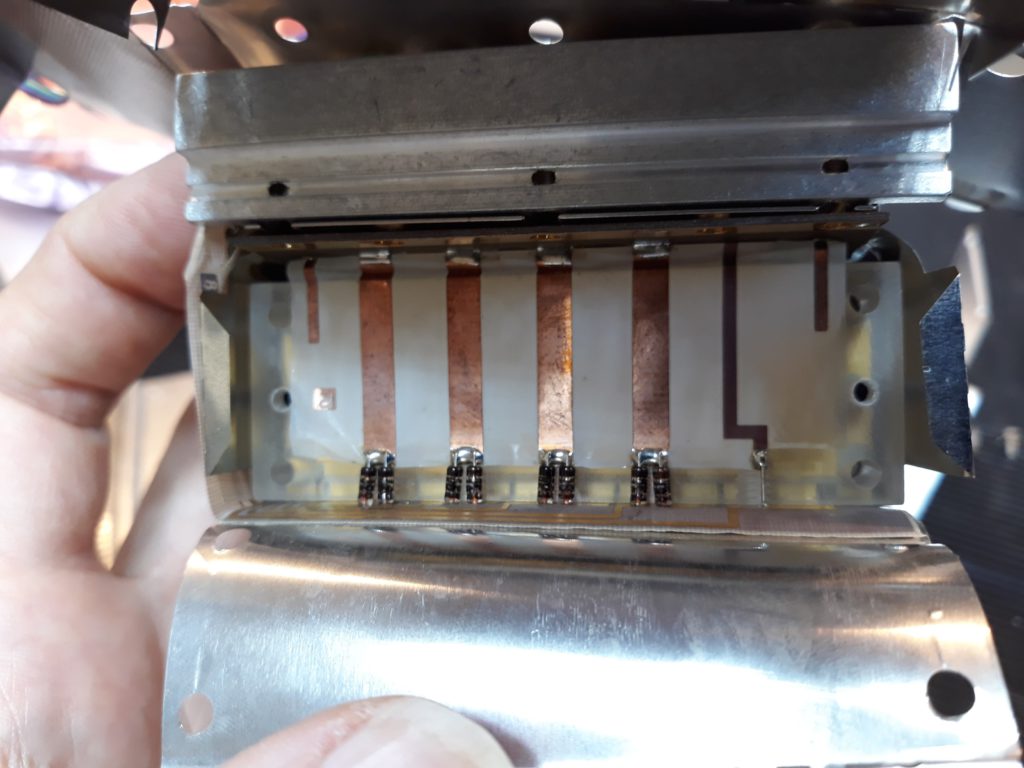

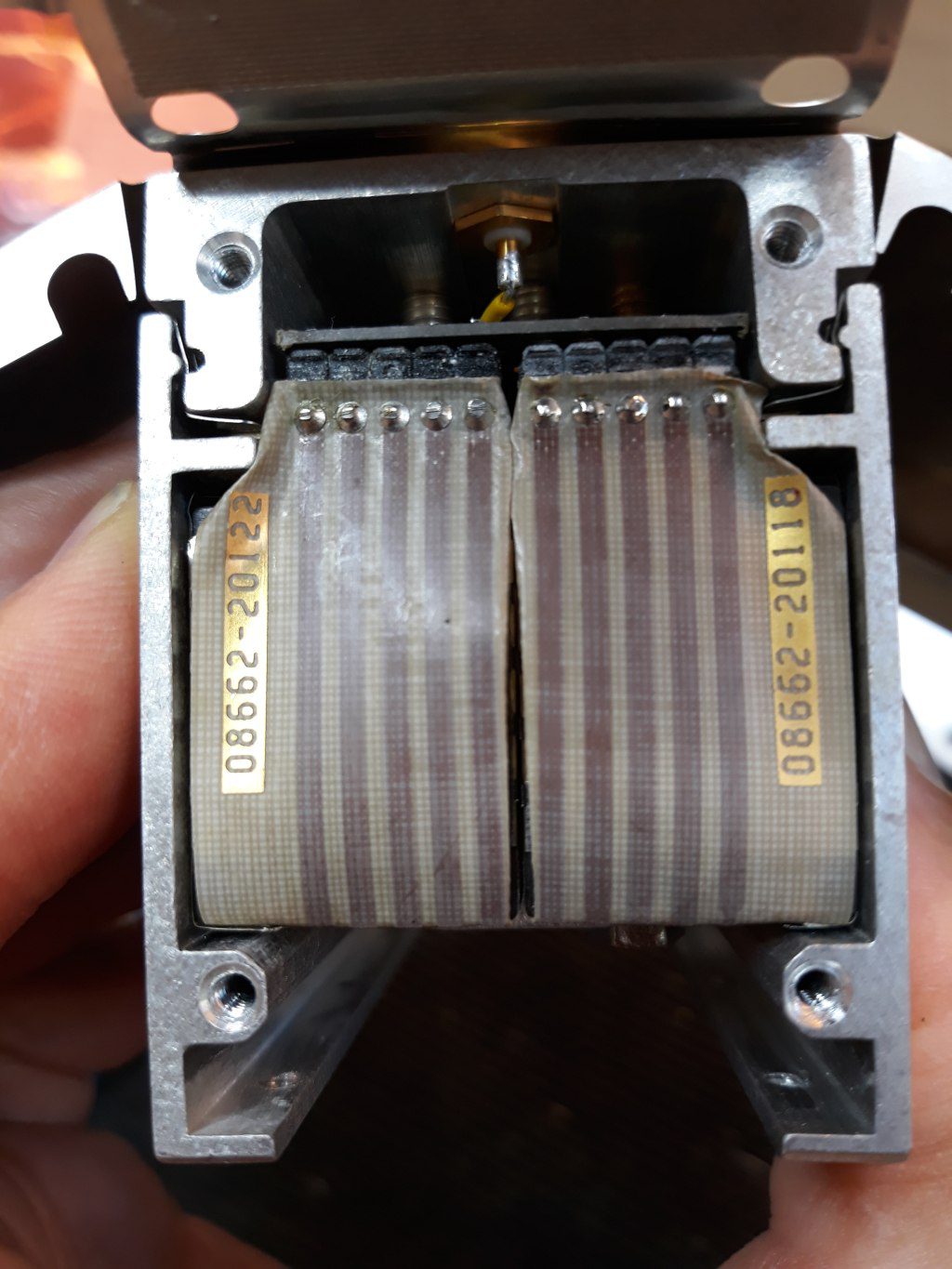

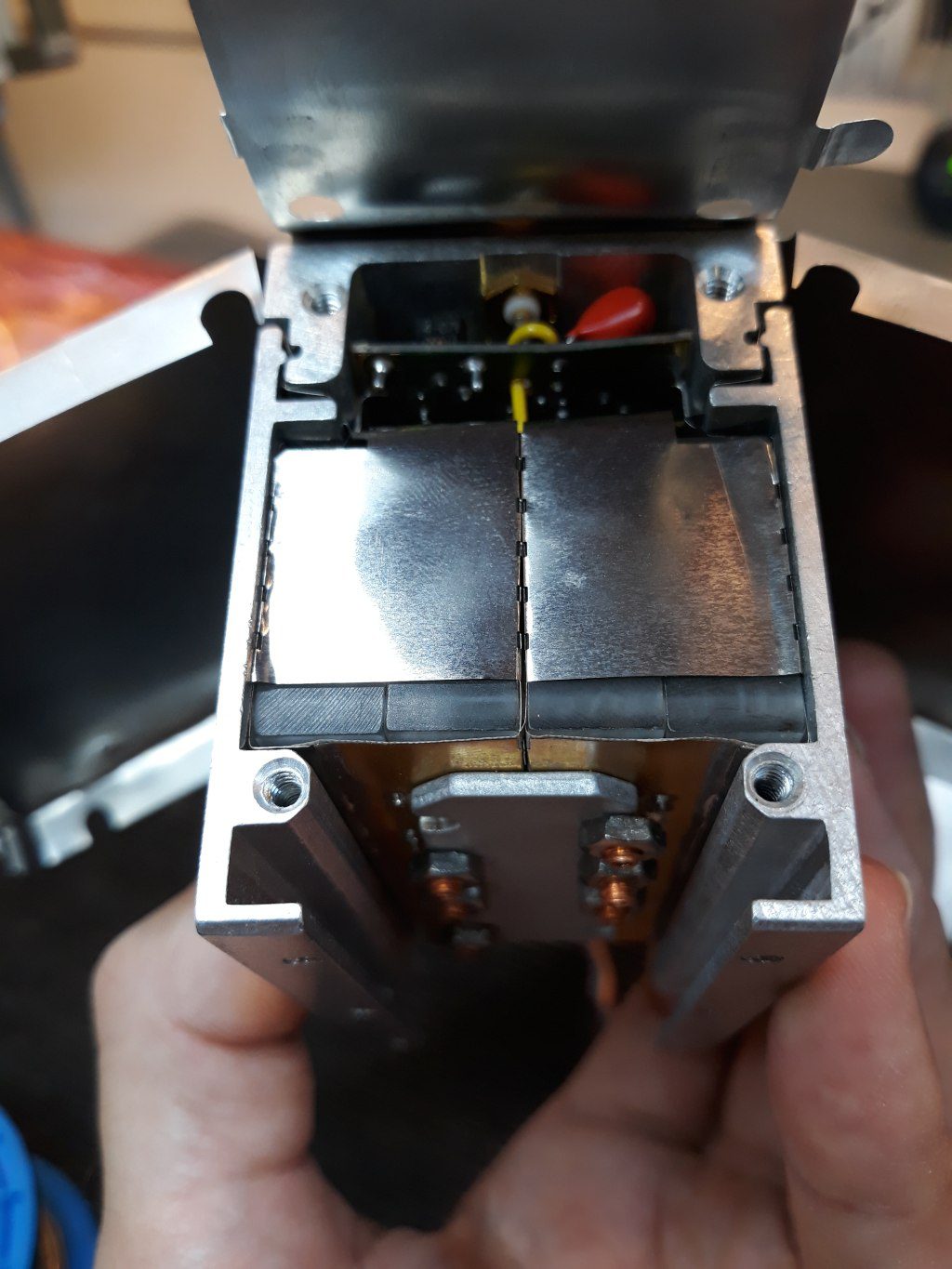

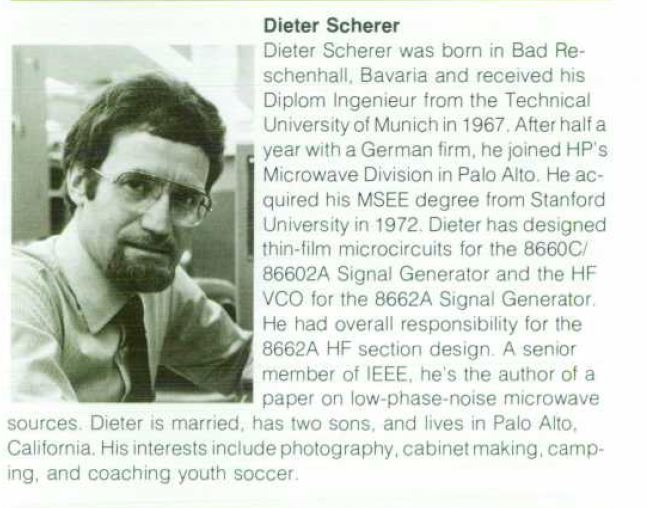

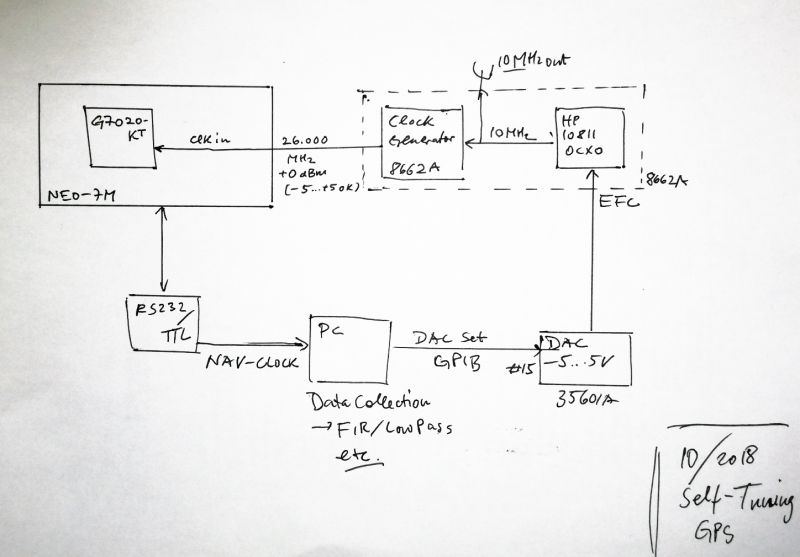

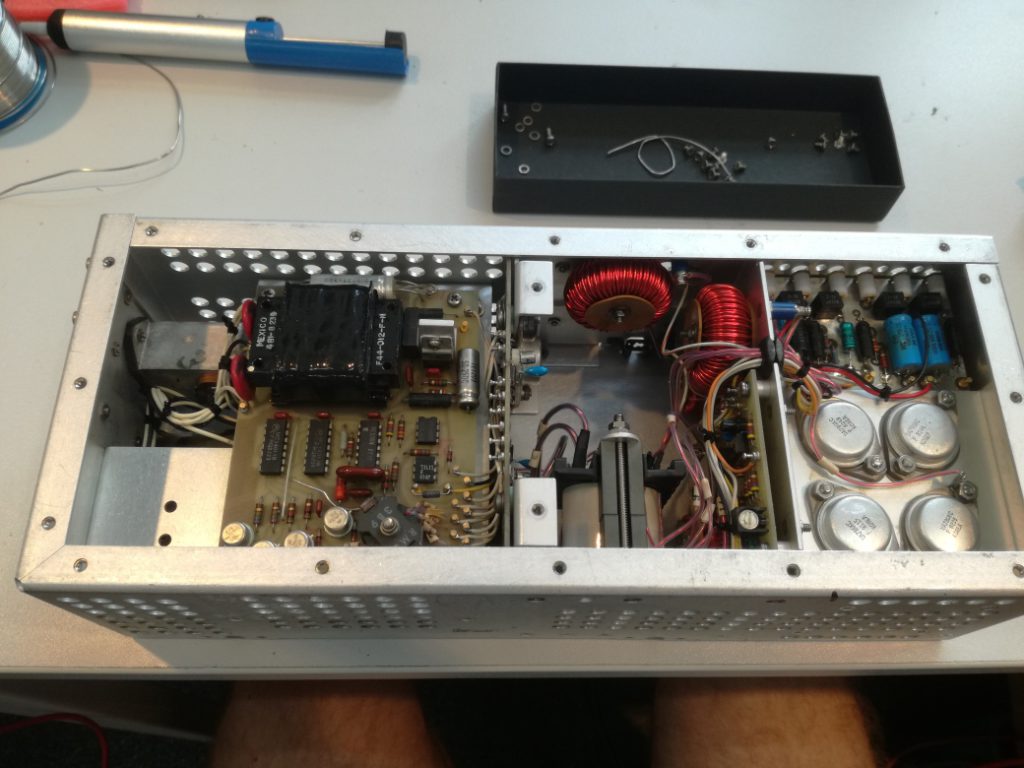

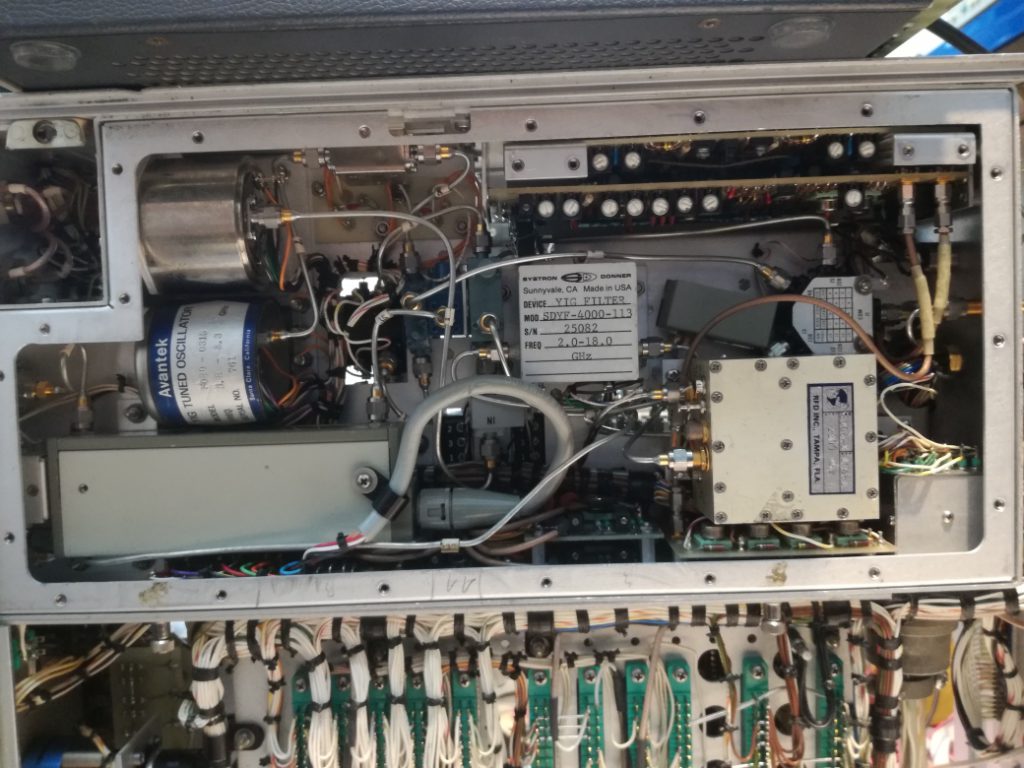

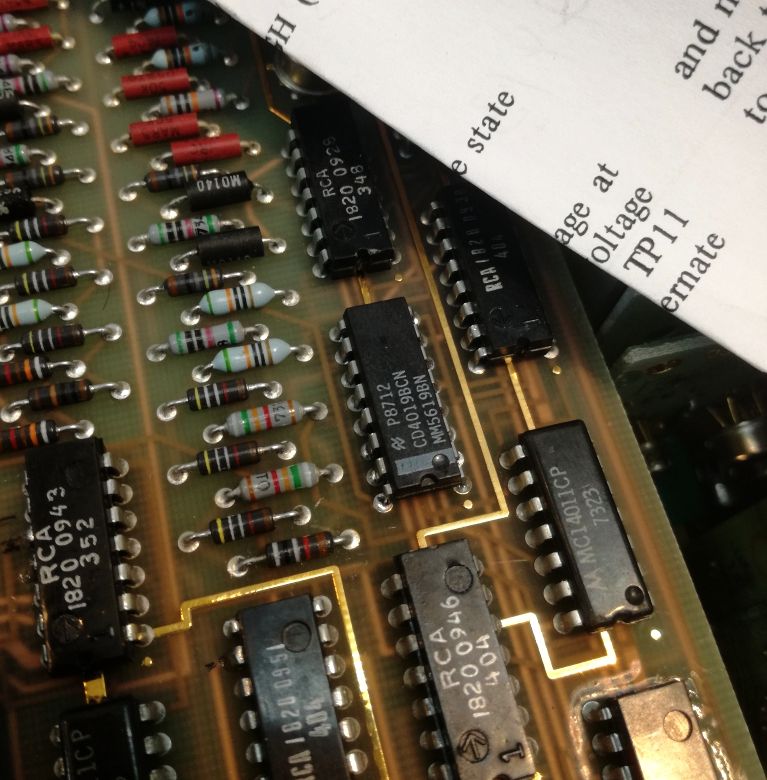

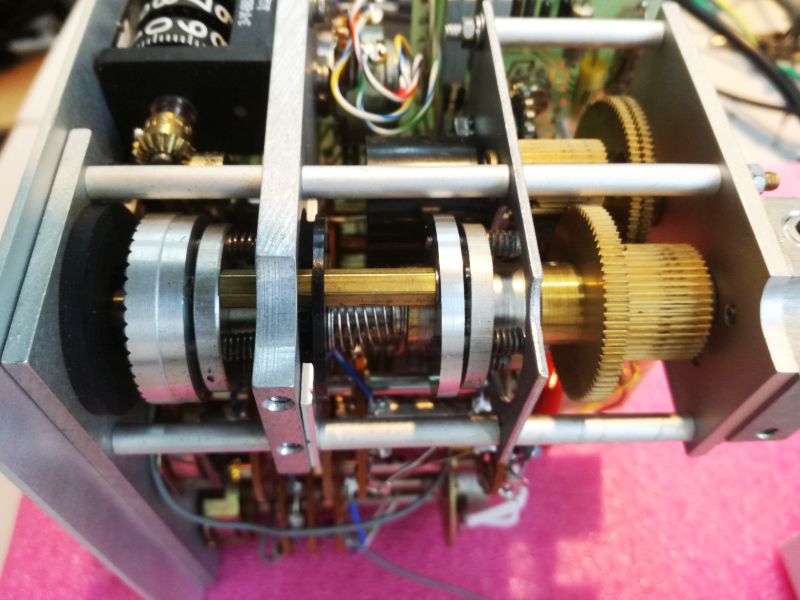

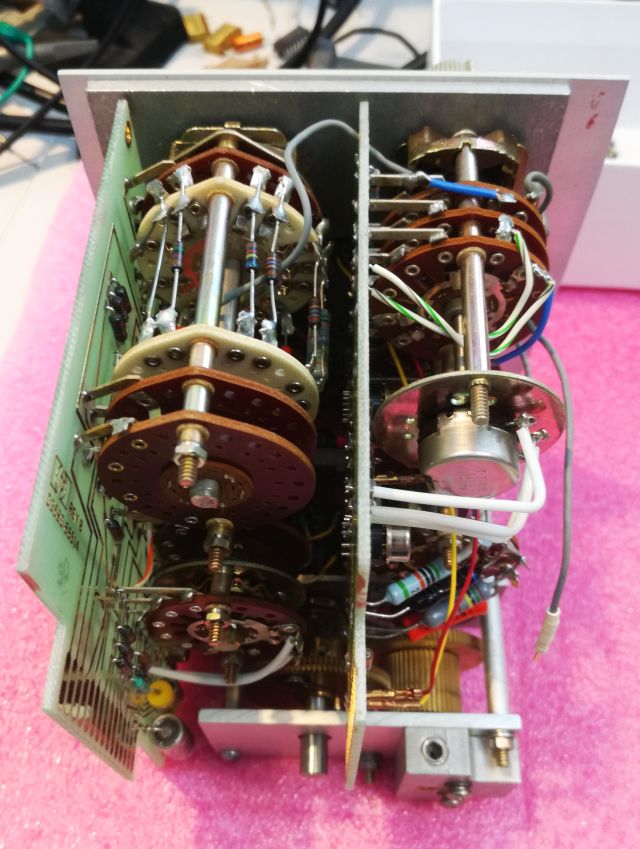

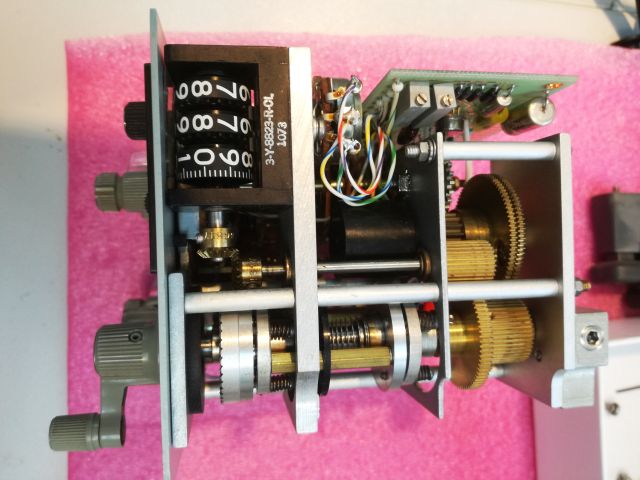

(2) With the Si5351A driven by a OCXO (HP 10811A, part of a 8662A unit – will be later replaced by a stand-alone unit using a HP 10811A with power supply and distribution amplifier, but essentially, to the same effect).

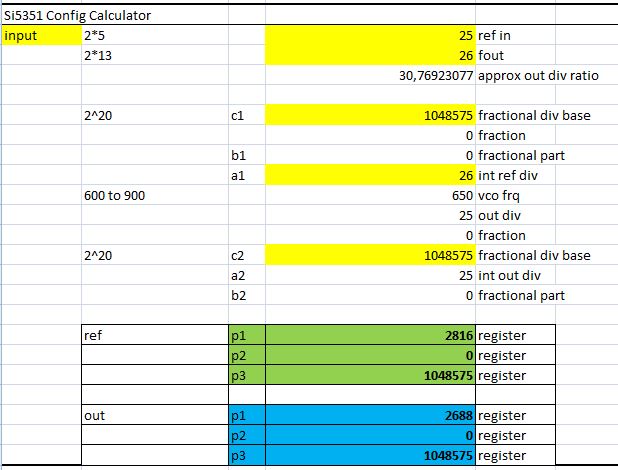

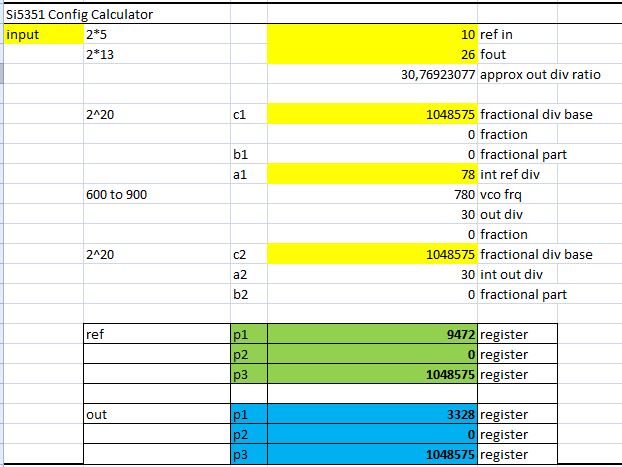

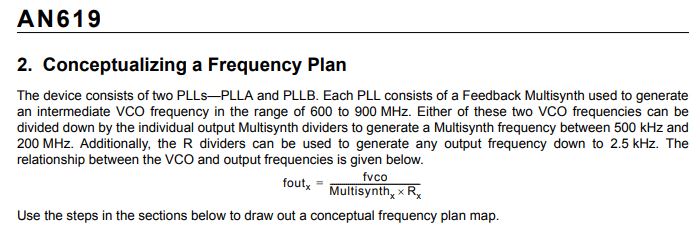

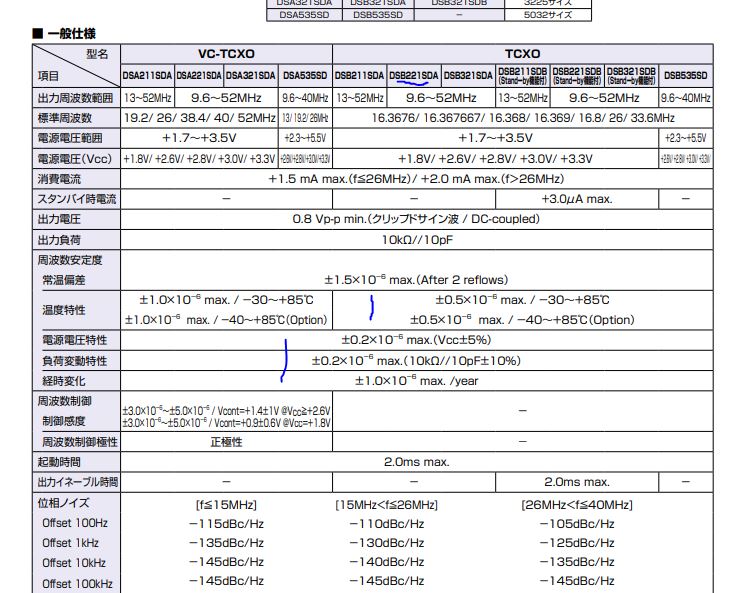

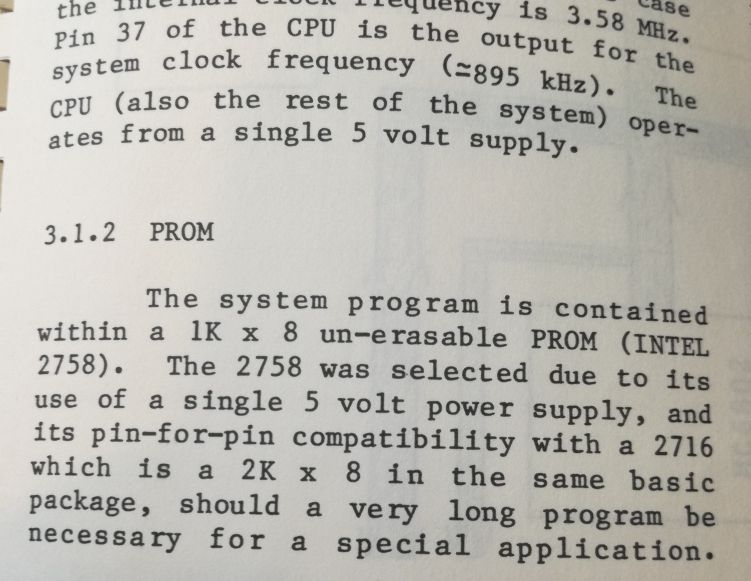

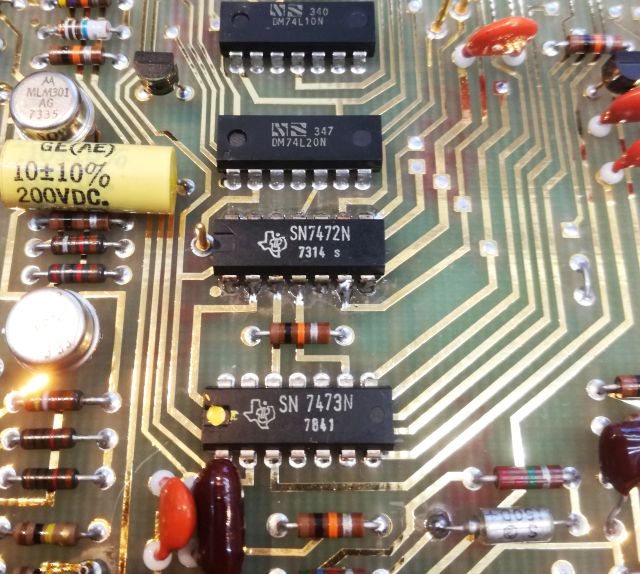

The first test, we need to set the registers of the Si5351A (check the Silicon Labs AN 618 Application Note – check it in a quiet hour, because it has a lot of heavy content…). 25 MHz clock input, 26 MHz OSC0 output – can be achieved by running the VCO at 650 MHz, and integer-only dividers.

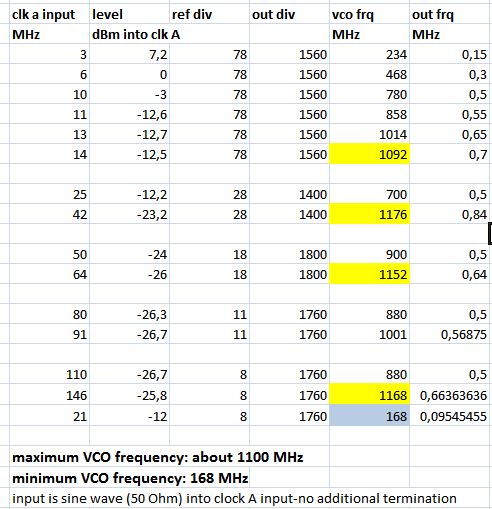

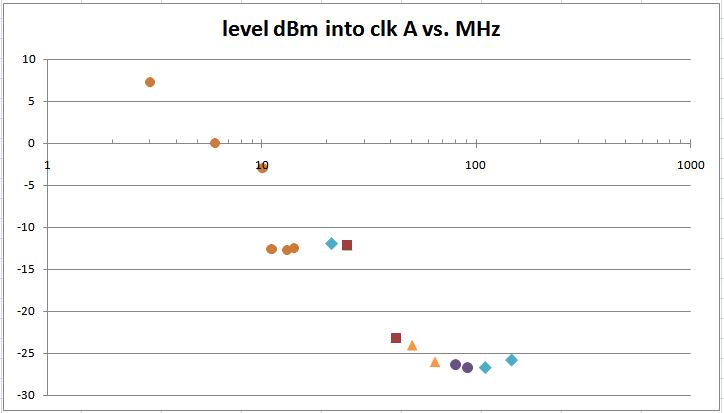

For the calculation, I use a self-made Excel sheet, which allows me to play around with the numbers to figure out the best combination of dividers and VCO frequency.

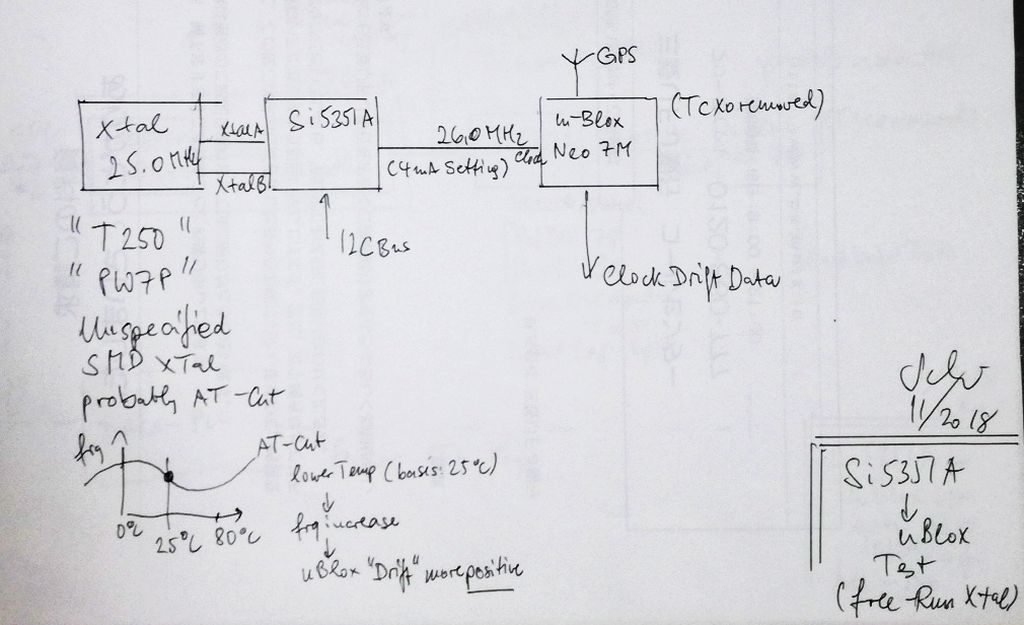

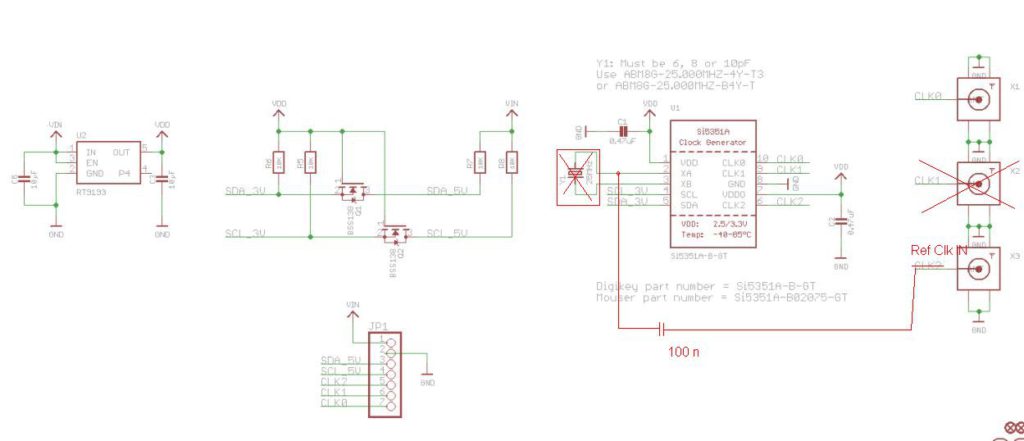

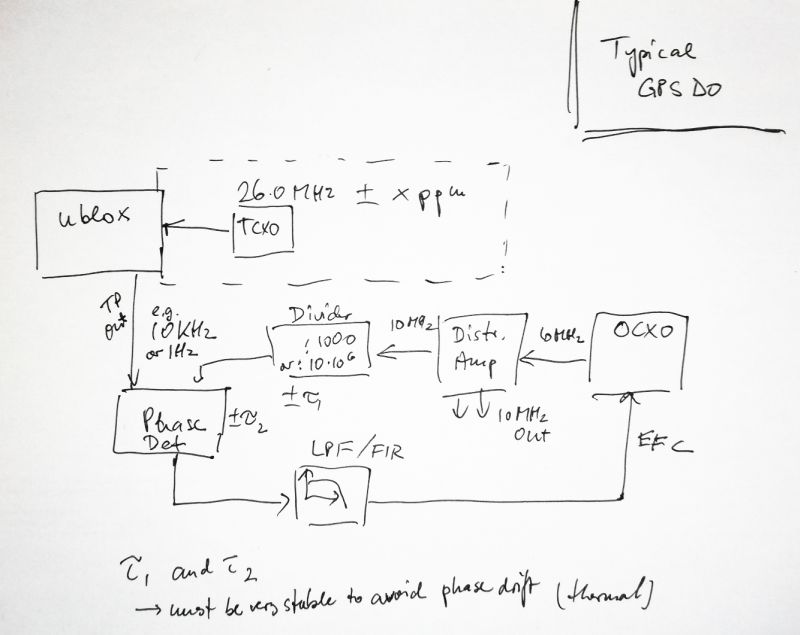

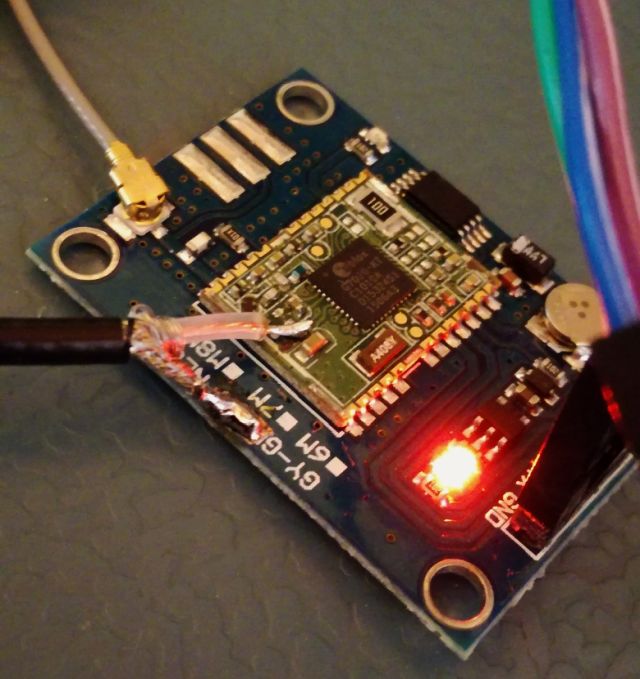

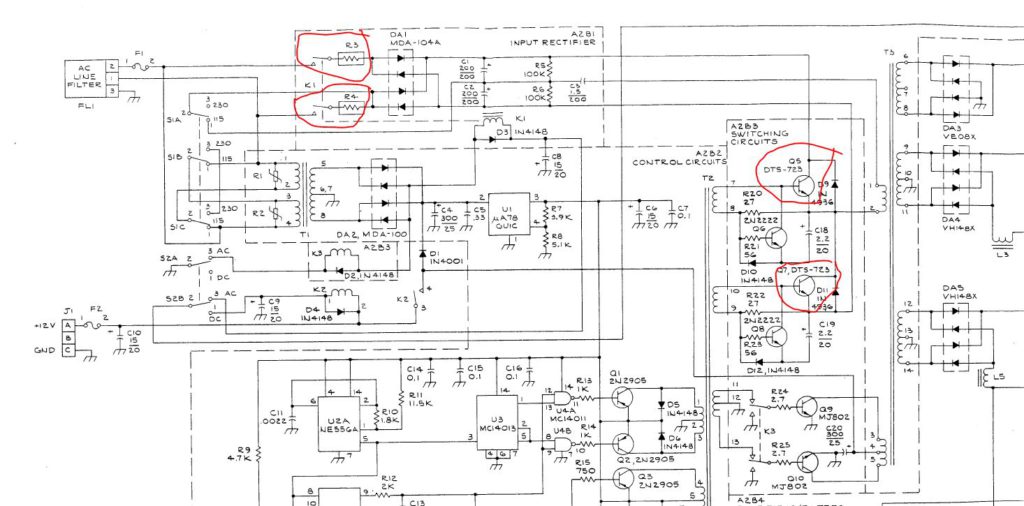

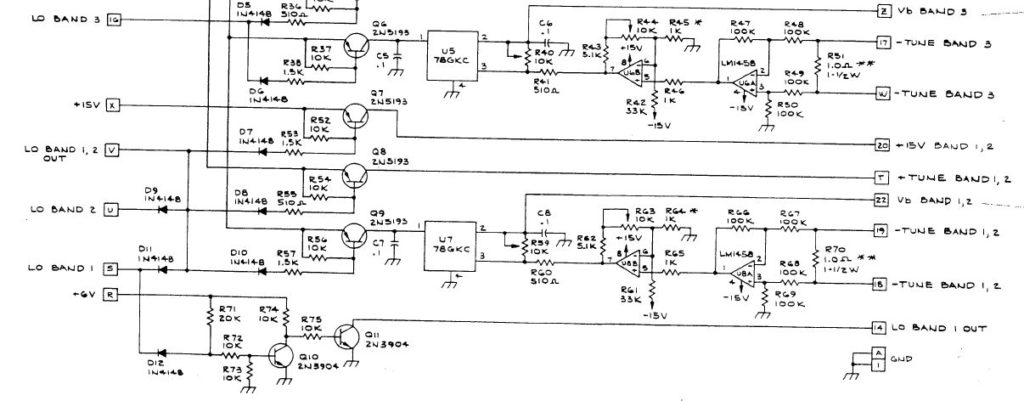

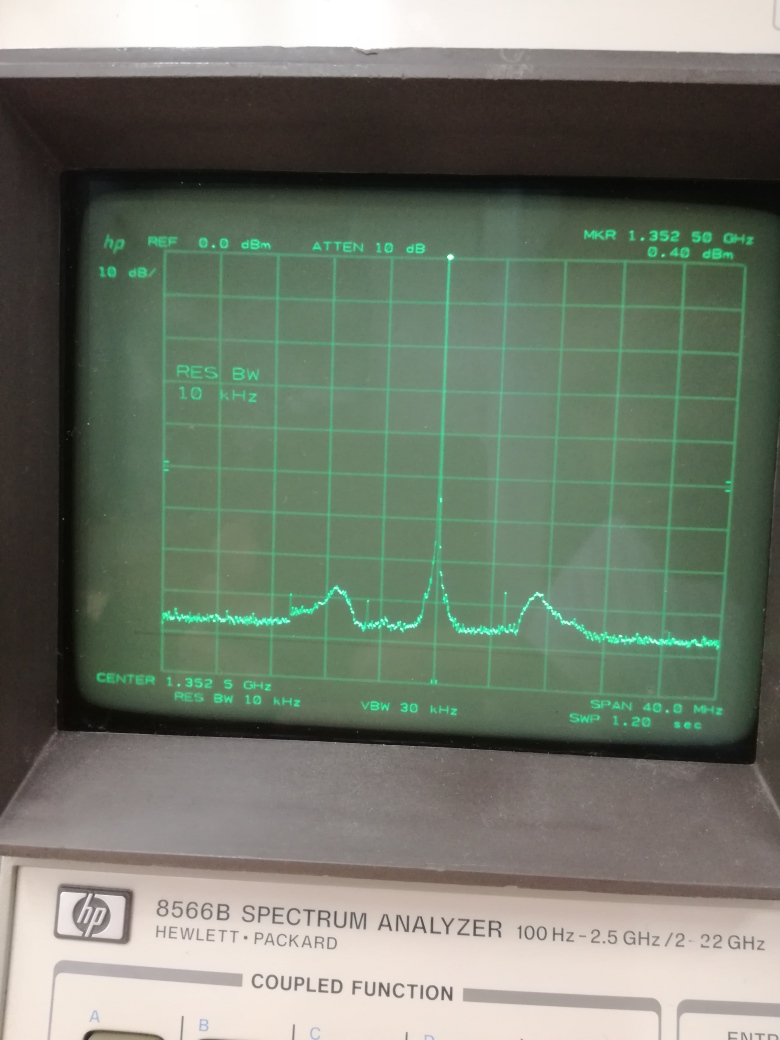

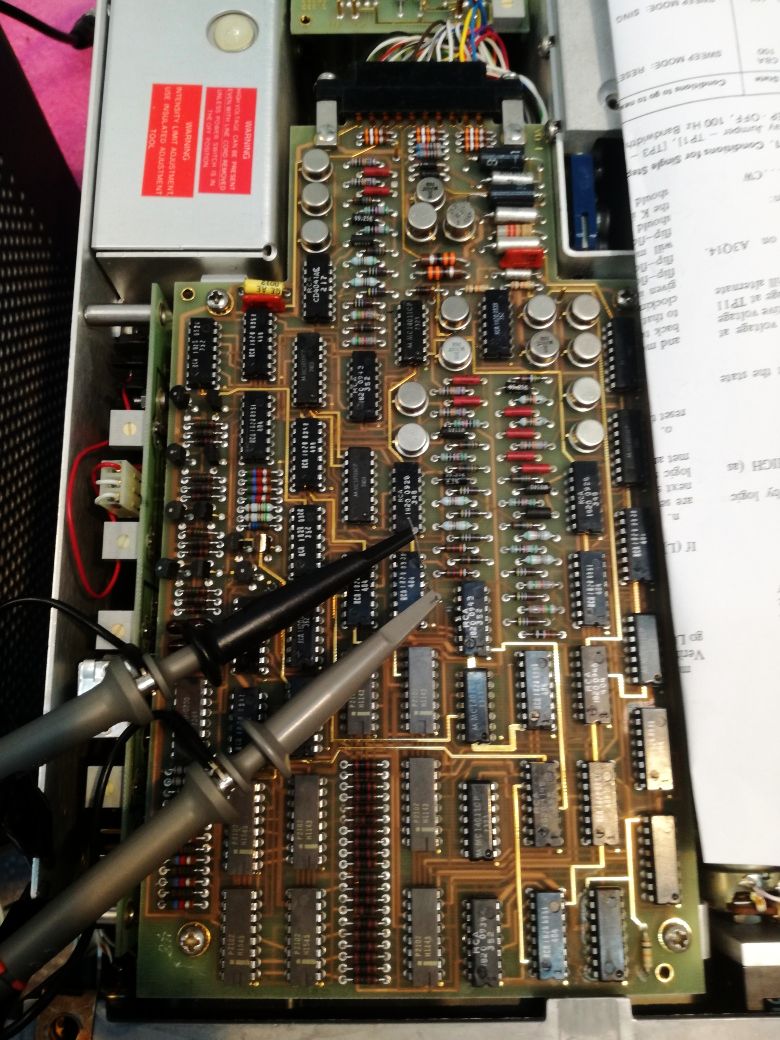

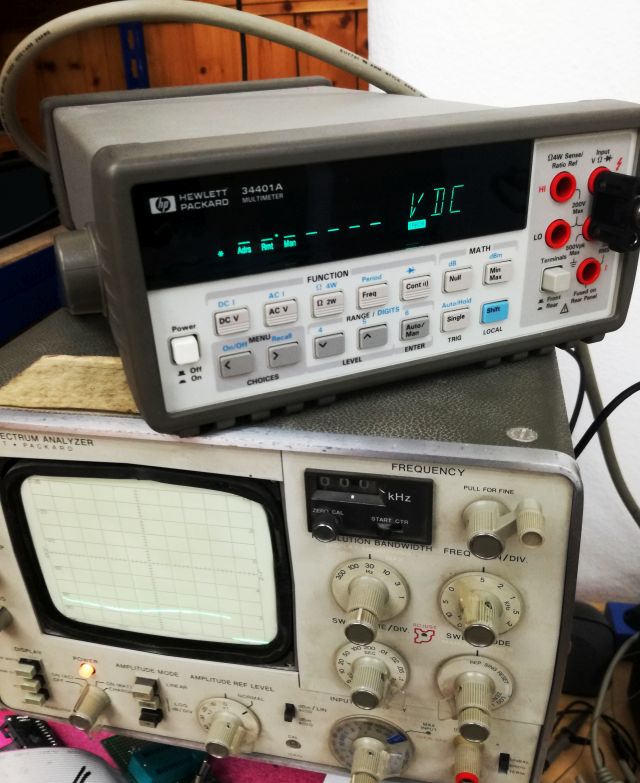

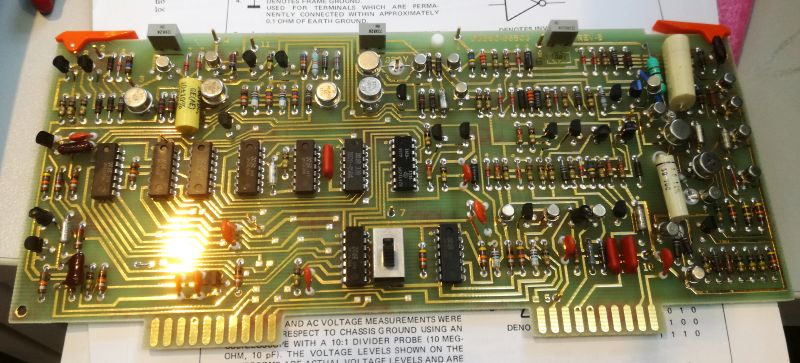

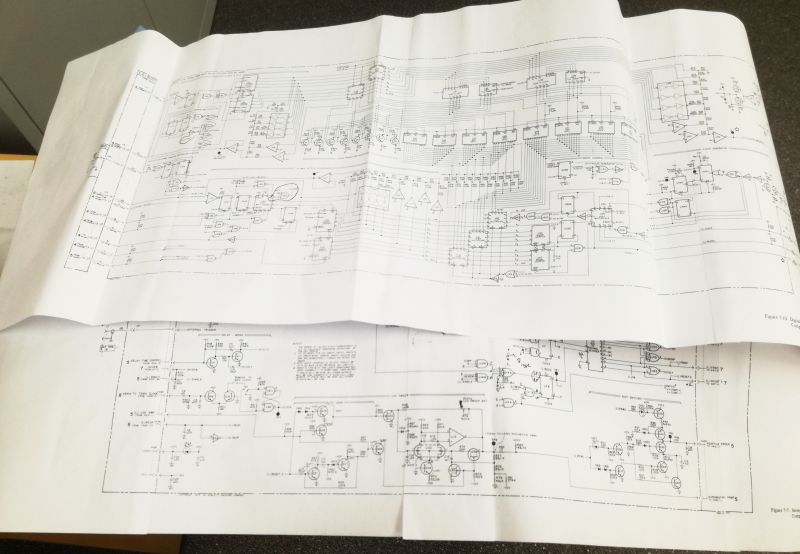

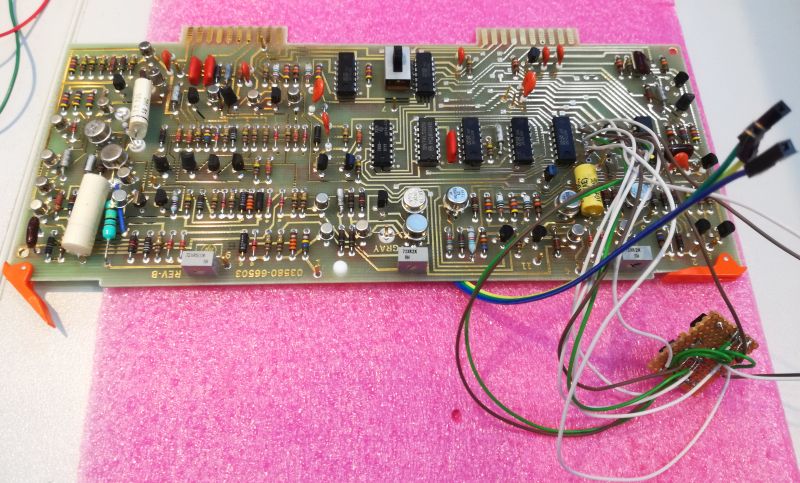

Here, the over test setup:

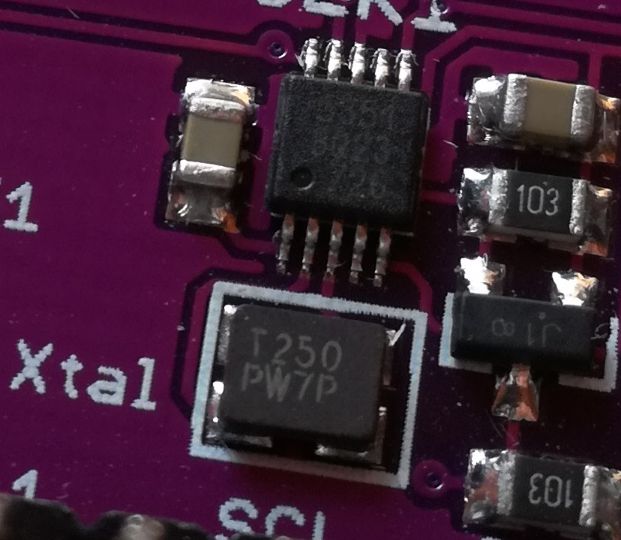

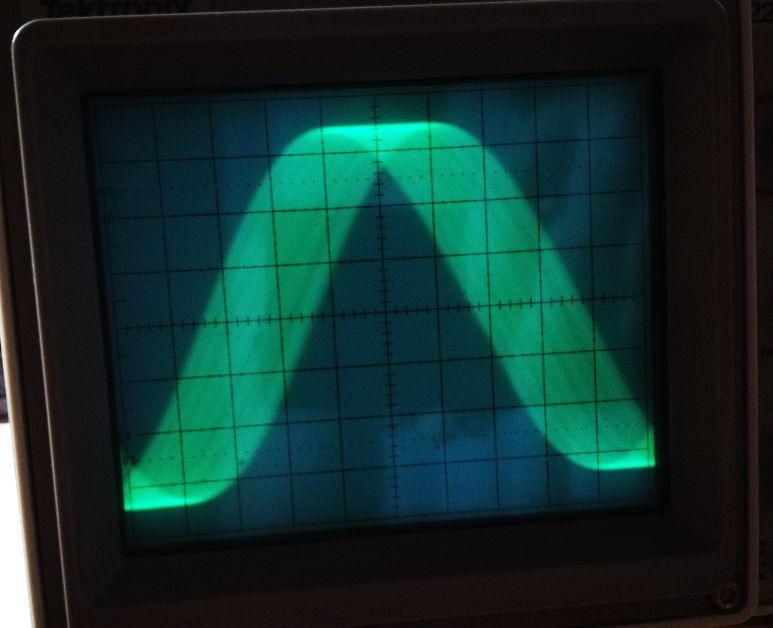

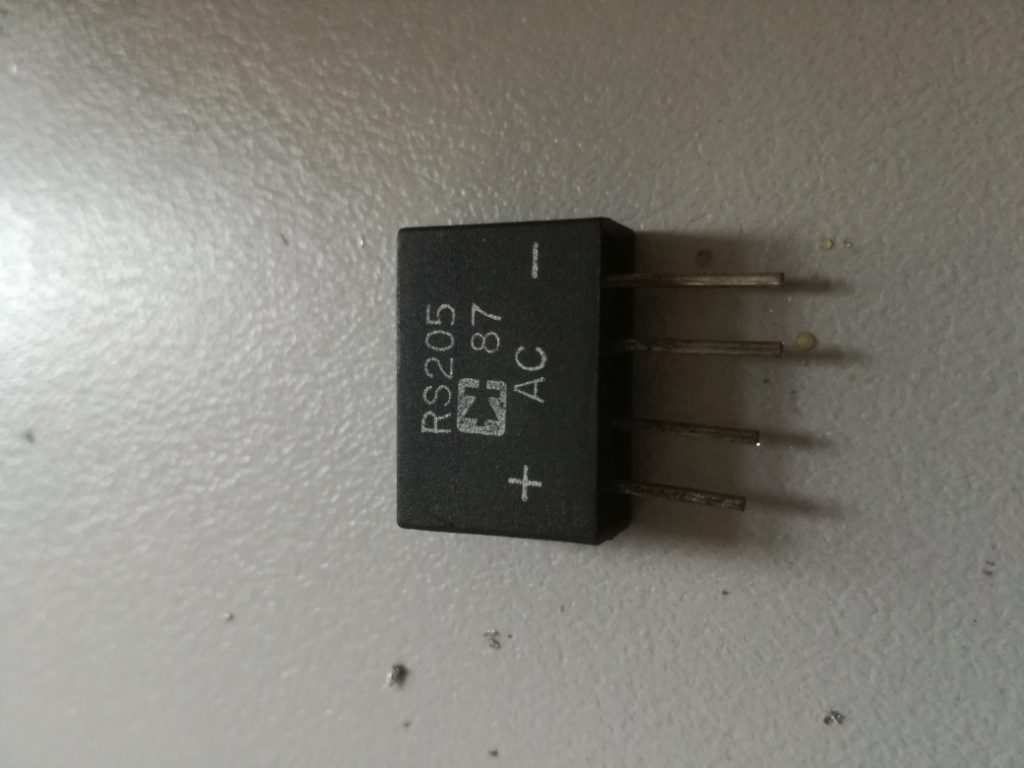

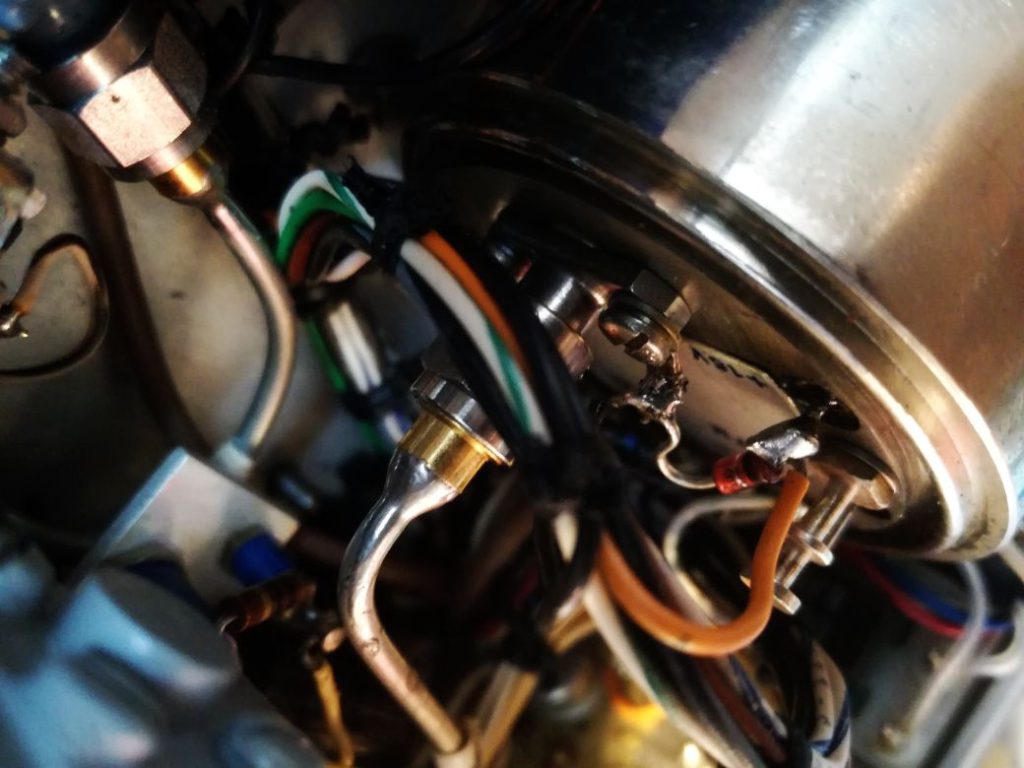

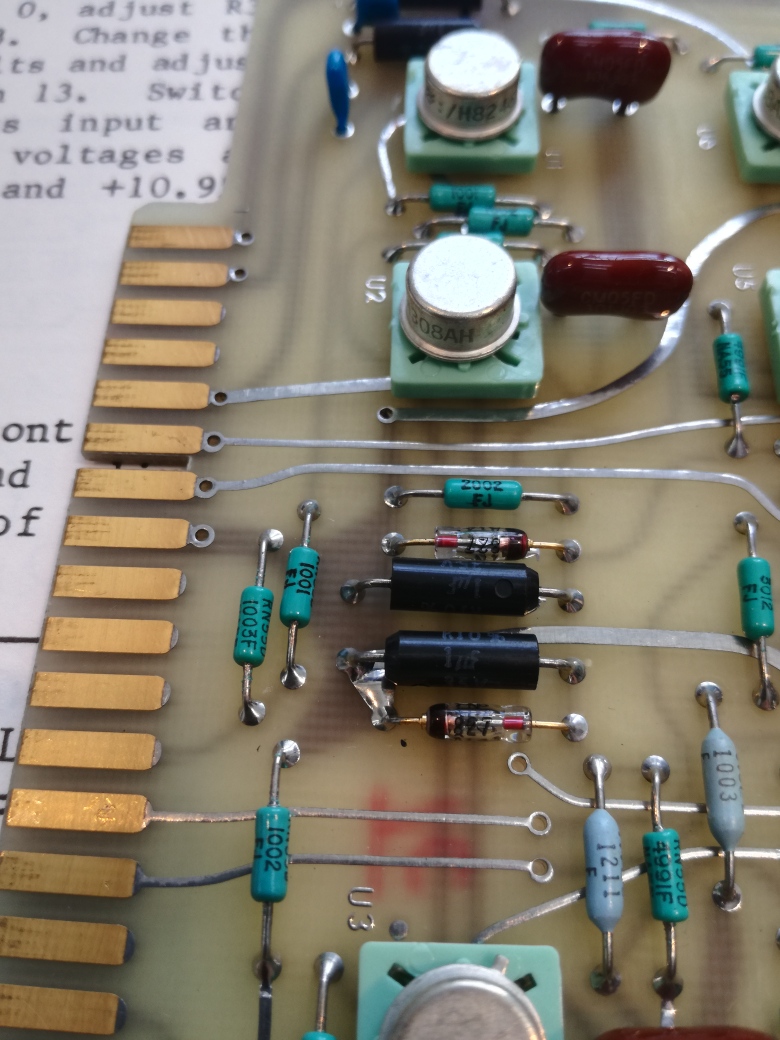

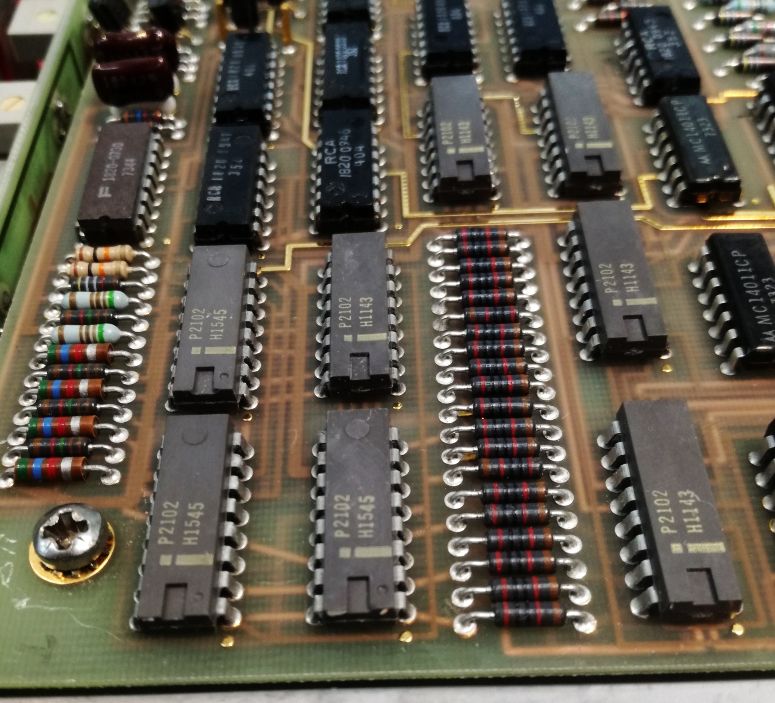

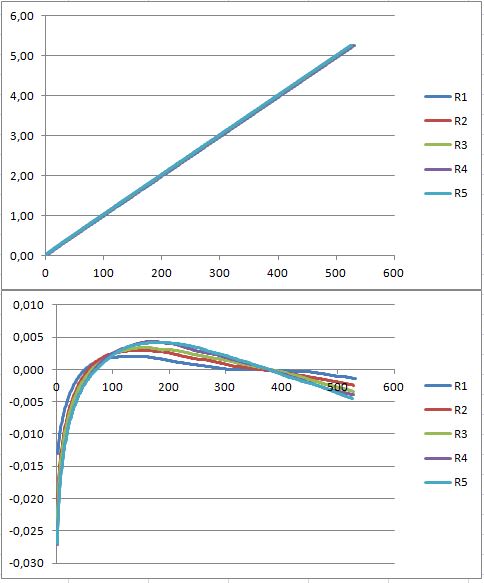

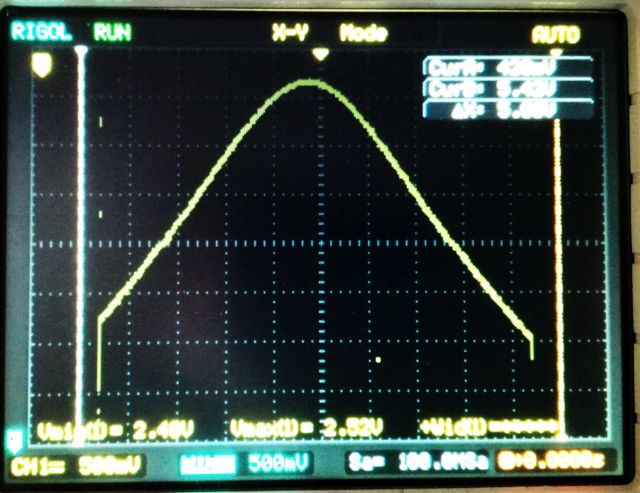

That’s the Xtal used – it came with the board, and I couldn’t find any data on it. Appears to be an AT cut crystal. Starting from room temperature, frequency, will go down with increasing temperature, and up with colder temperatures.

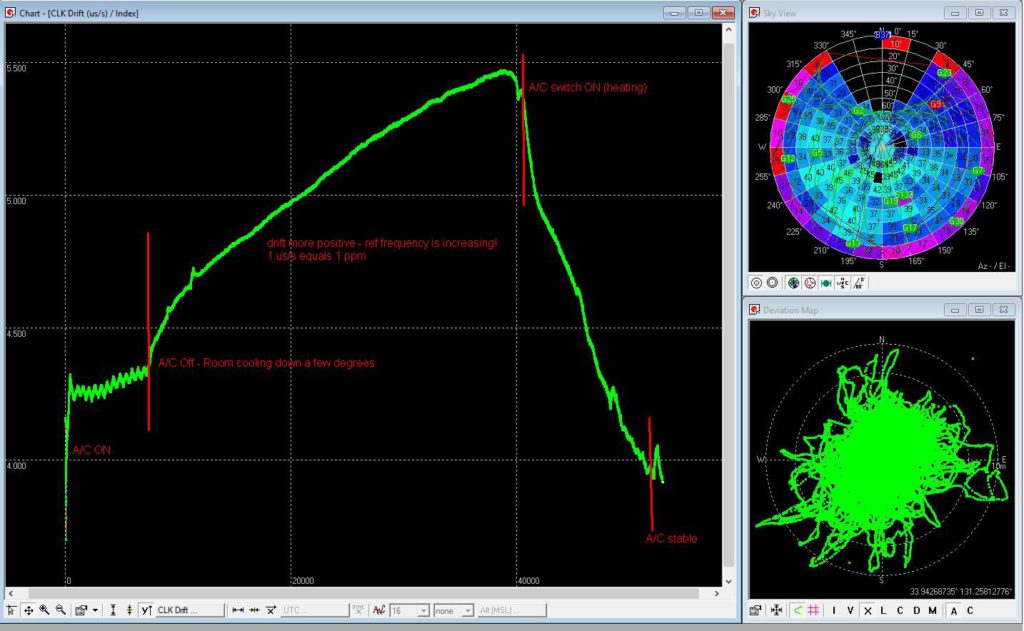

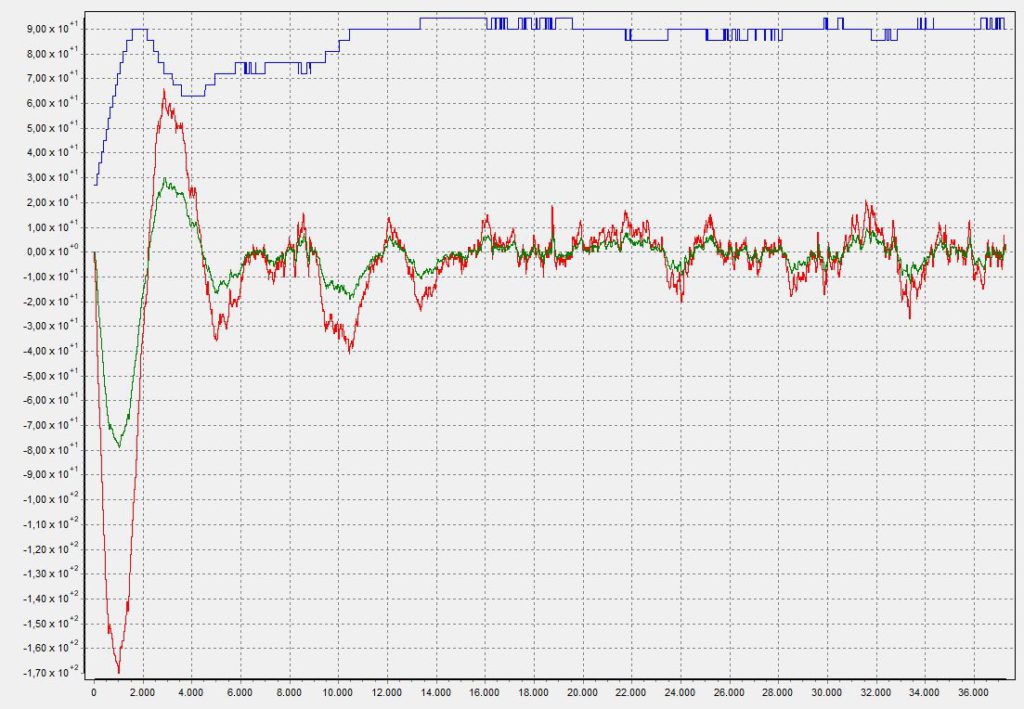

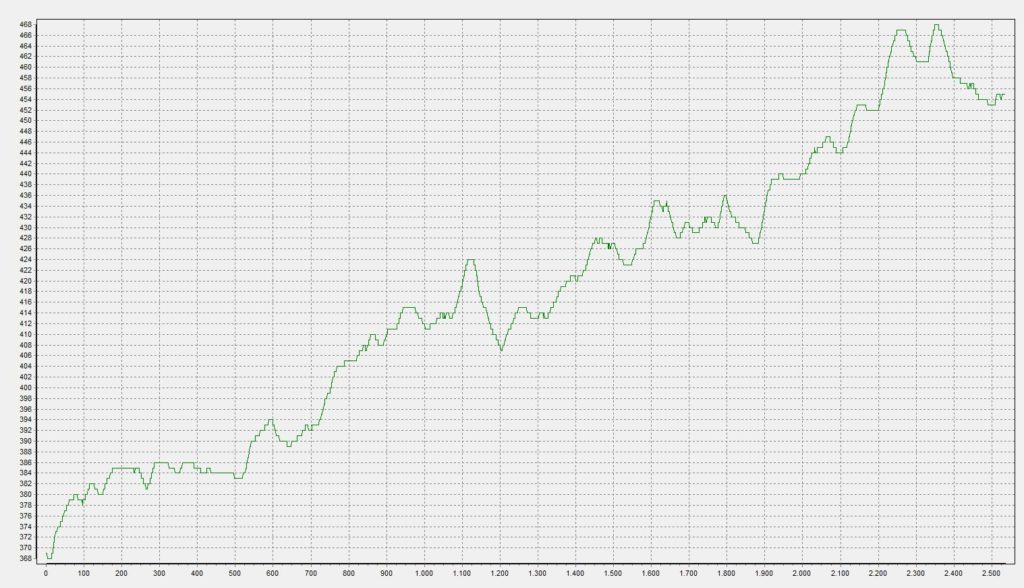

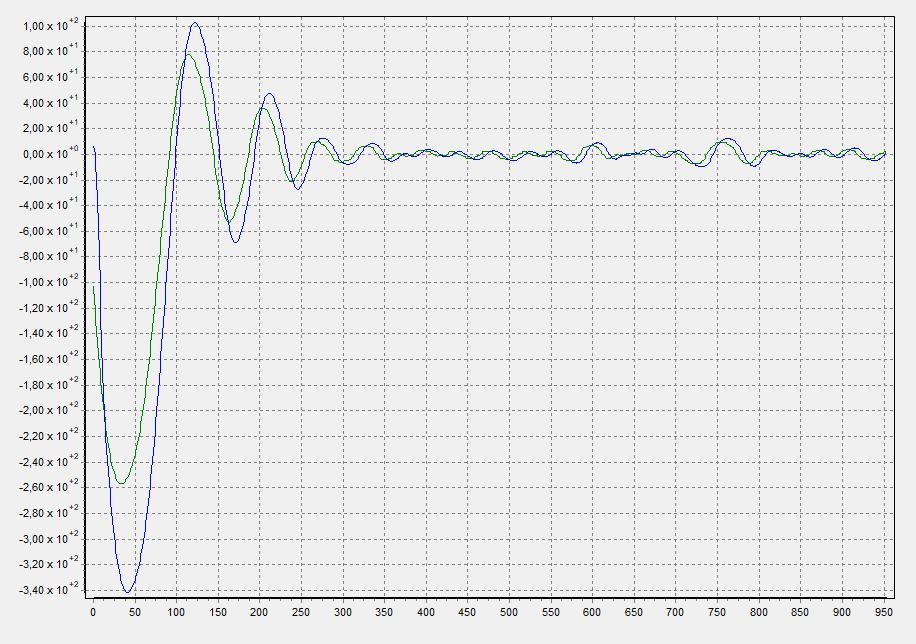

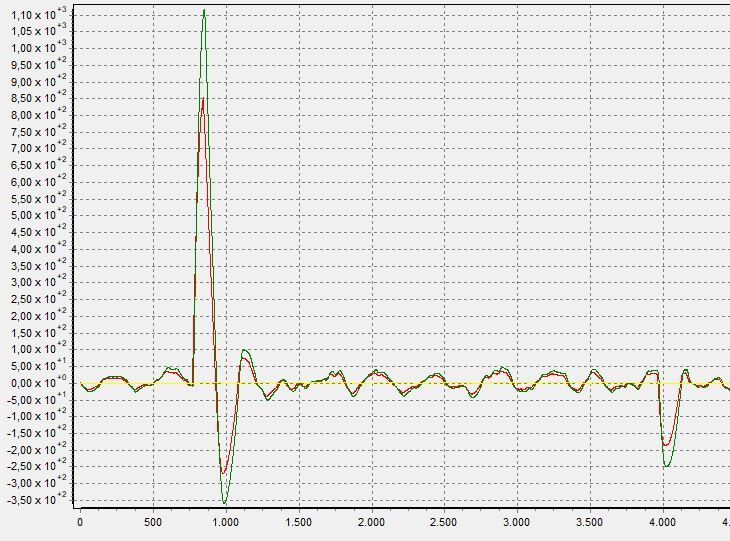

Such temperature variation is easily introduced here in Japan. First, keeping the room at 22 degC by the aircon (A/C) unit, then switching it off overnight (cooling the room by a few degrees, maybe down to 17 degC), then, next morning, heating up again to 22 degC (and a bit more as we had a sunny day).

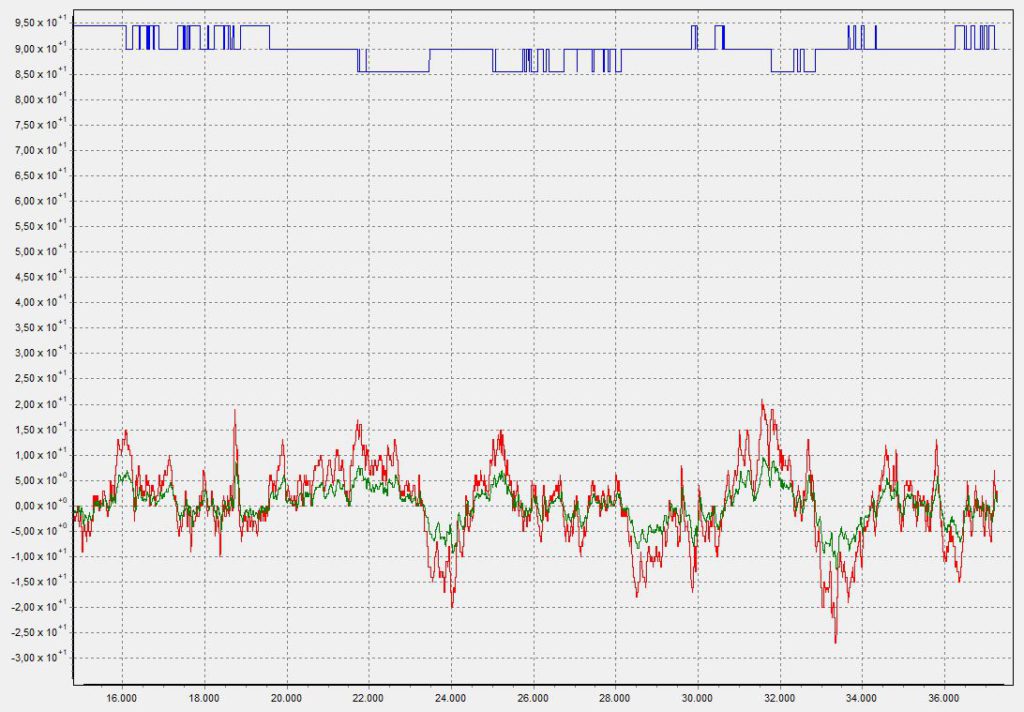

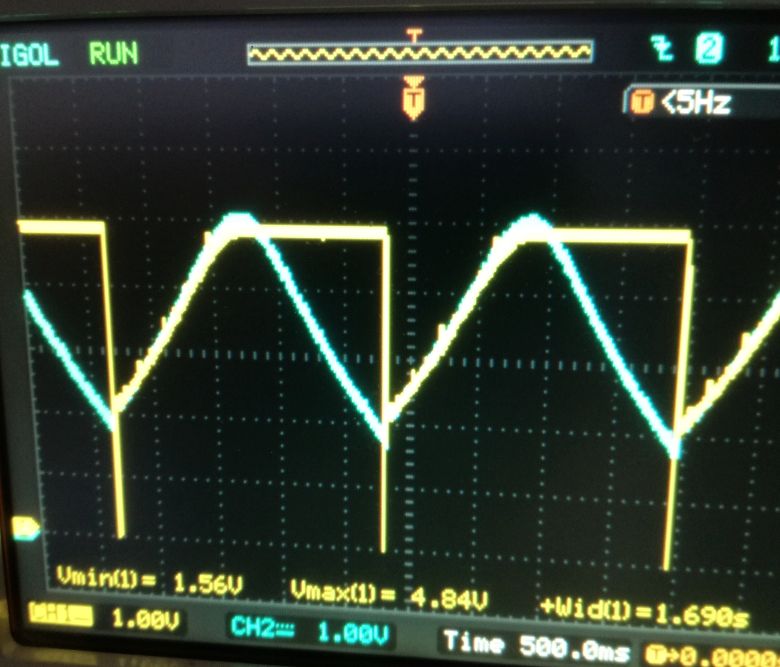

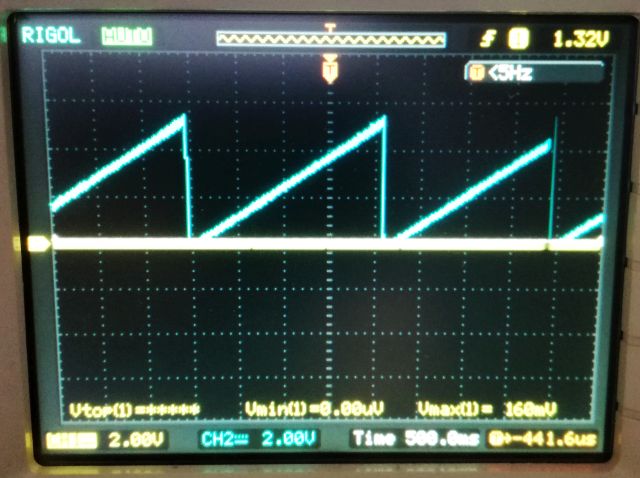

The detail below also shows the small thermal mass of the Si5351A, free-hanging in air. Better to enclose it or to add some thermal mass later, to avoid thermal-gradient introduced noise or instability. You can clearly see the on-off cycles of the A/C unit regulating the room temperature.

After all this study, we find out that we can use the GPS and Xtal as a quarz thermometer (such thermometers really exist!)!

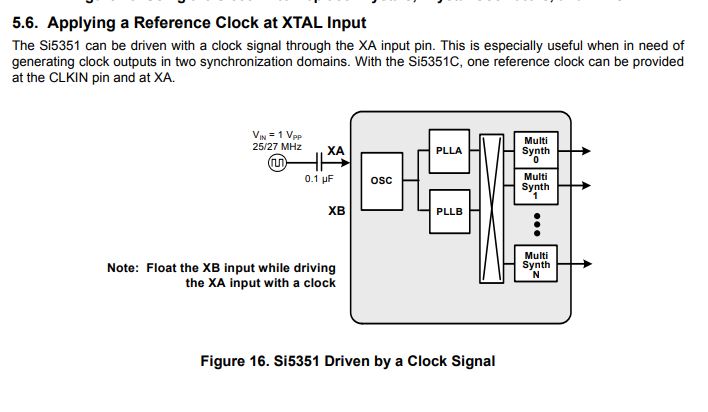

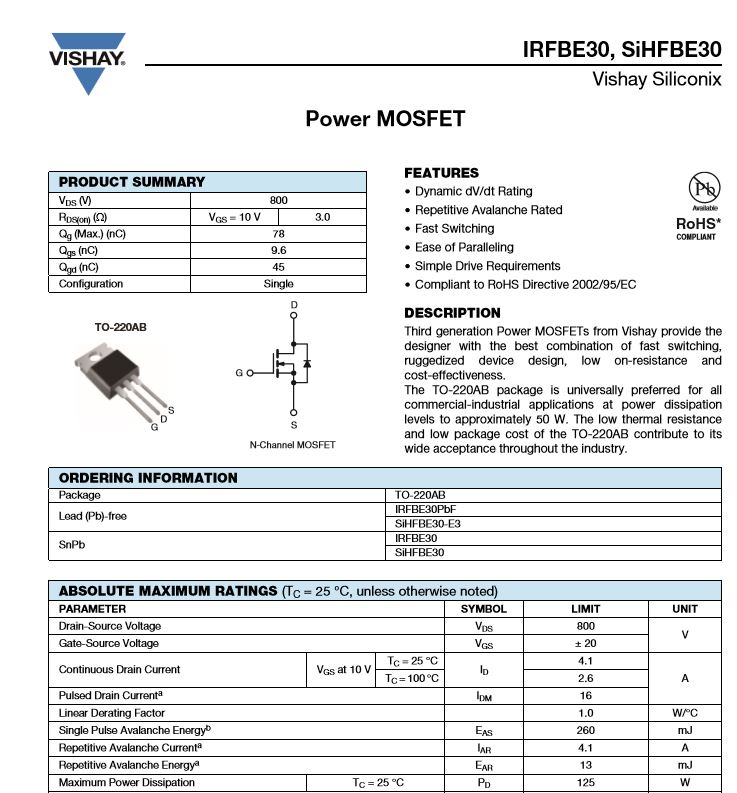

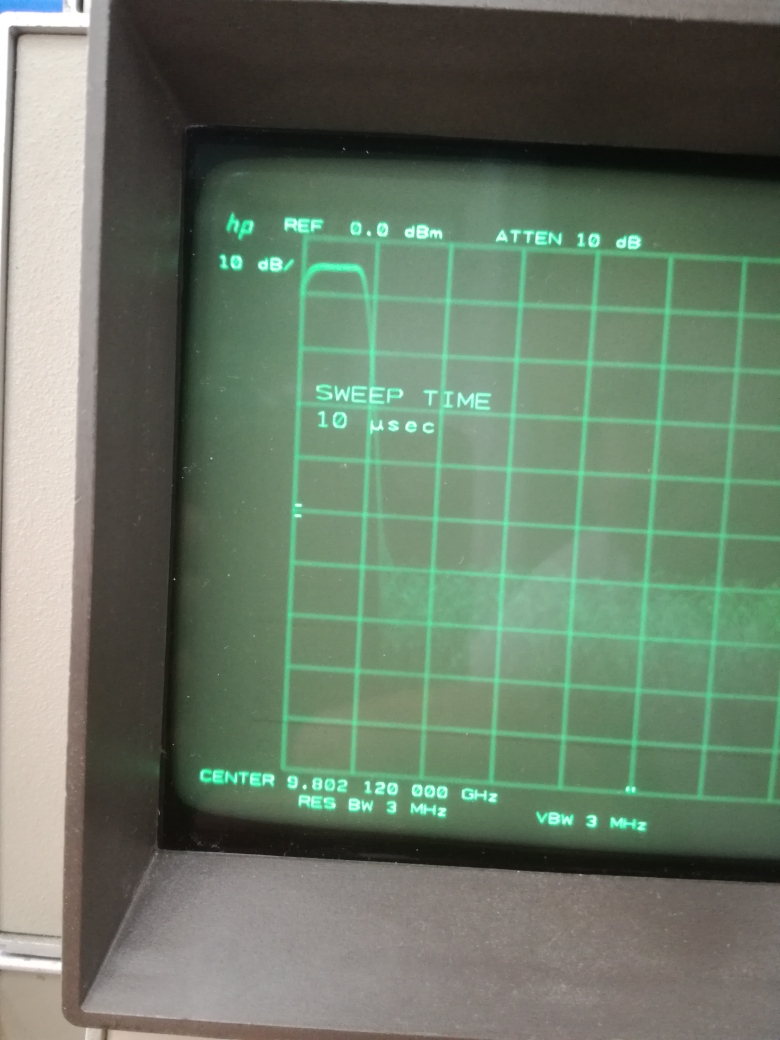

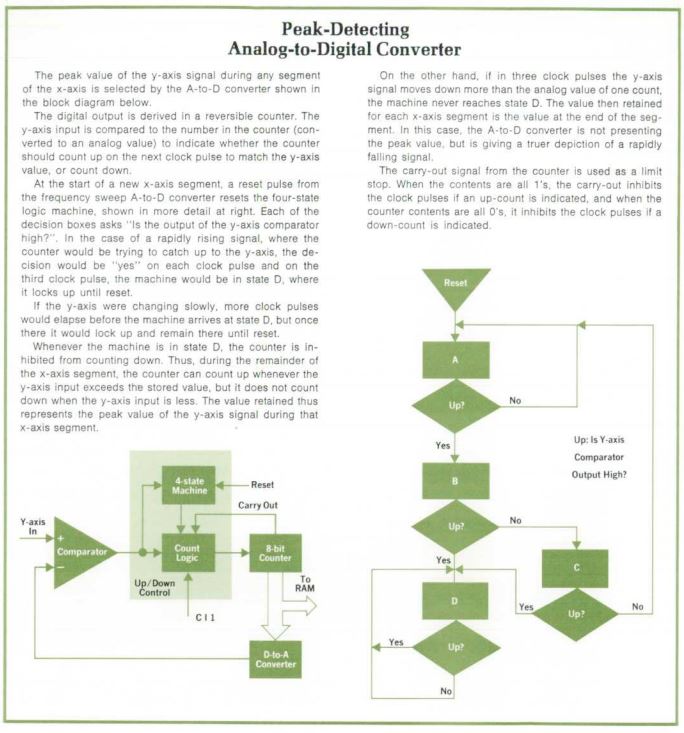

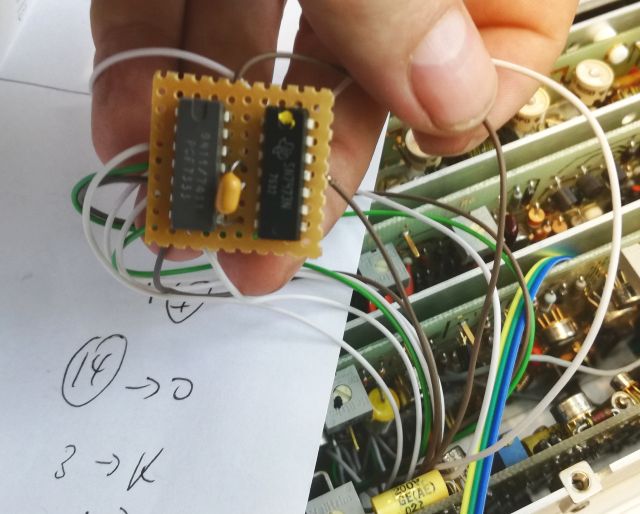

Test 2, now running with a 10 MHz reference clock, and still 26 MHz output to the u-blox M7 (in all cases, the u-Blox has been modified by removing the TCXO, and feeding the clock signal directly to the GPS chip). Sure I known that I am running the Si5351A outside of the specified range – but after all the research, Si5351A Spec, Myth and Truth, I believe this is OK.

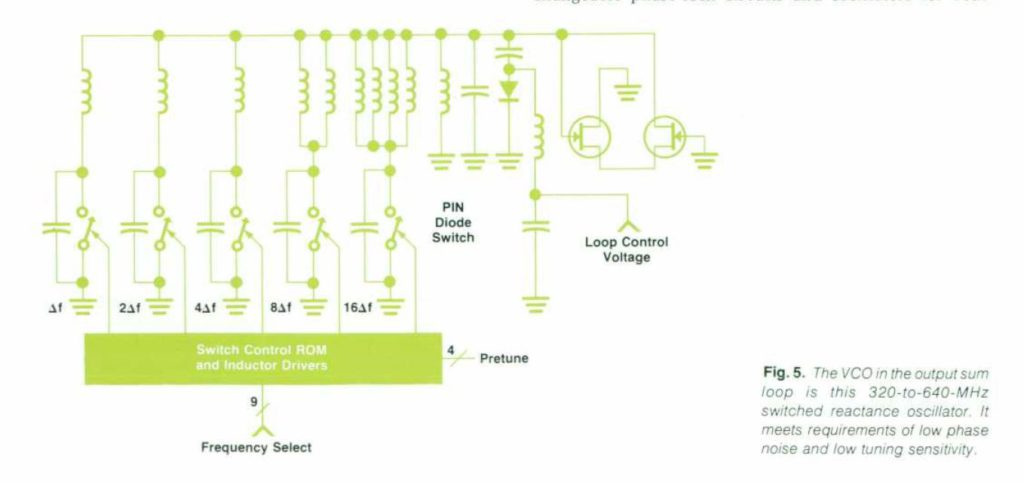

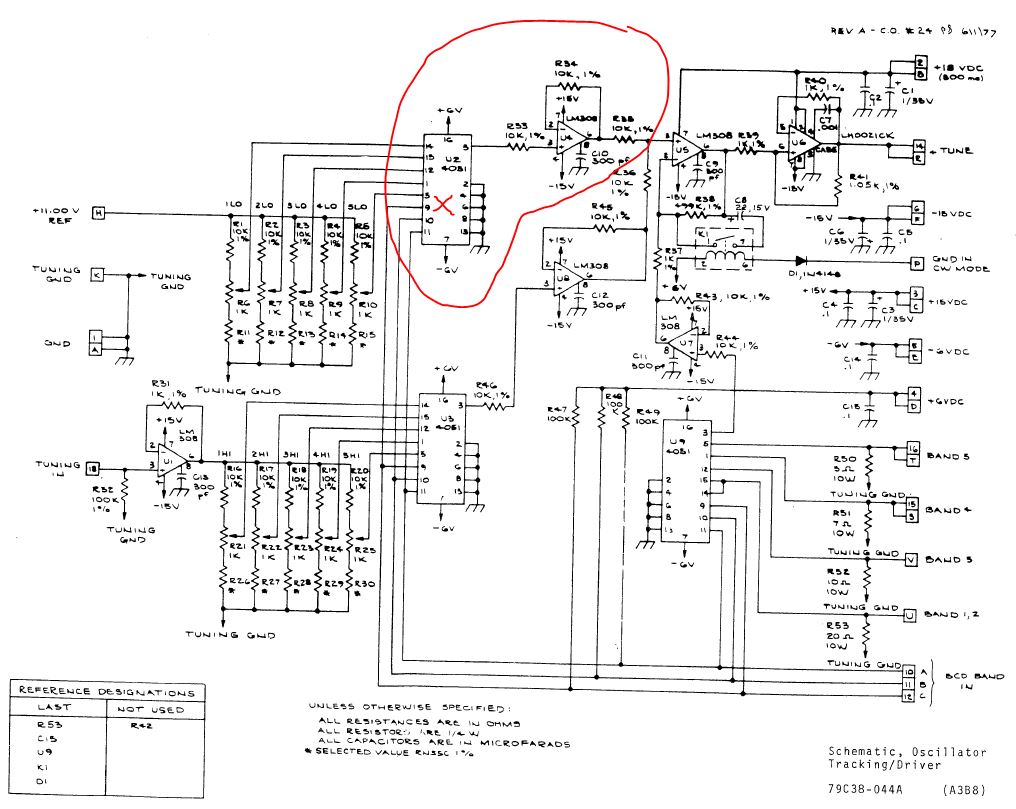

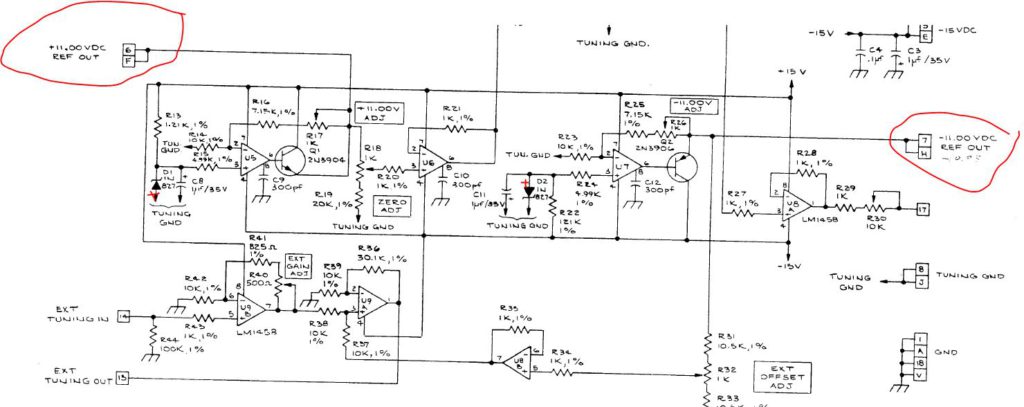

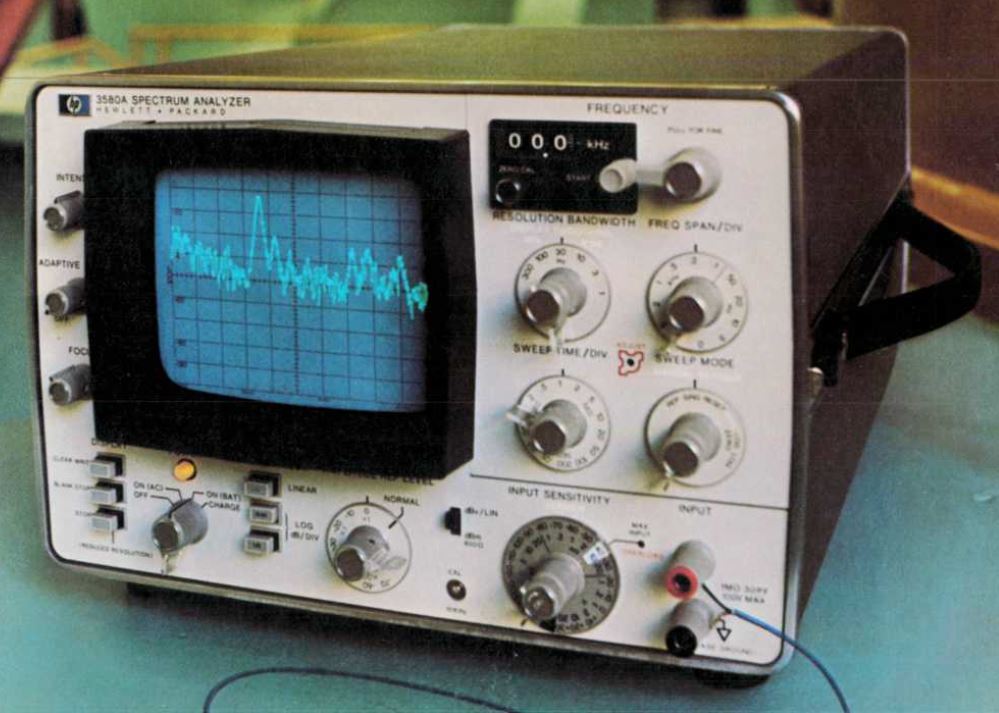

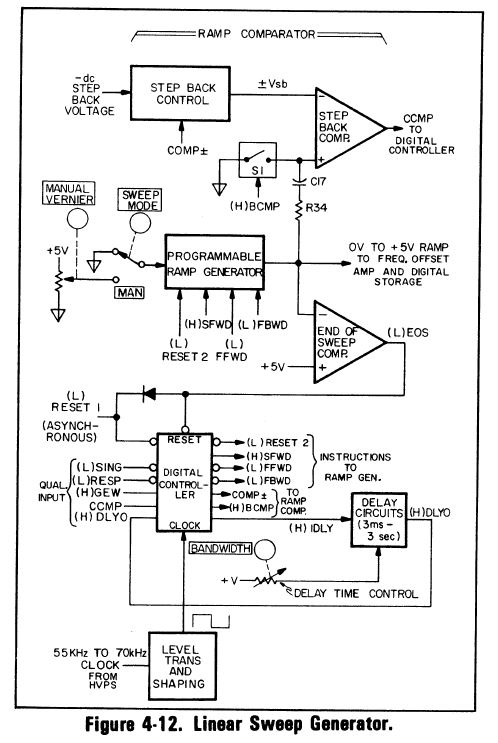

The test setup – note the dotted additions – this will be the later phase locked circuit.

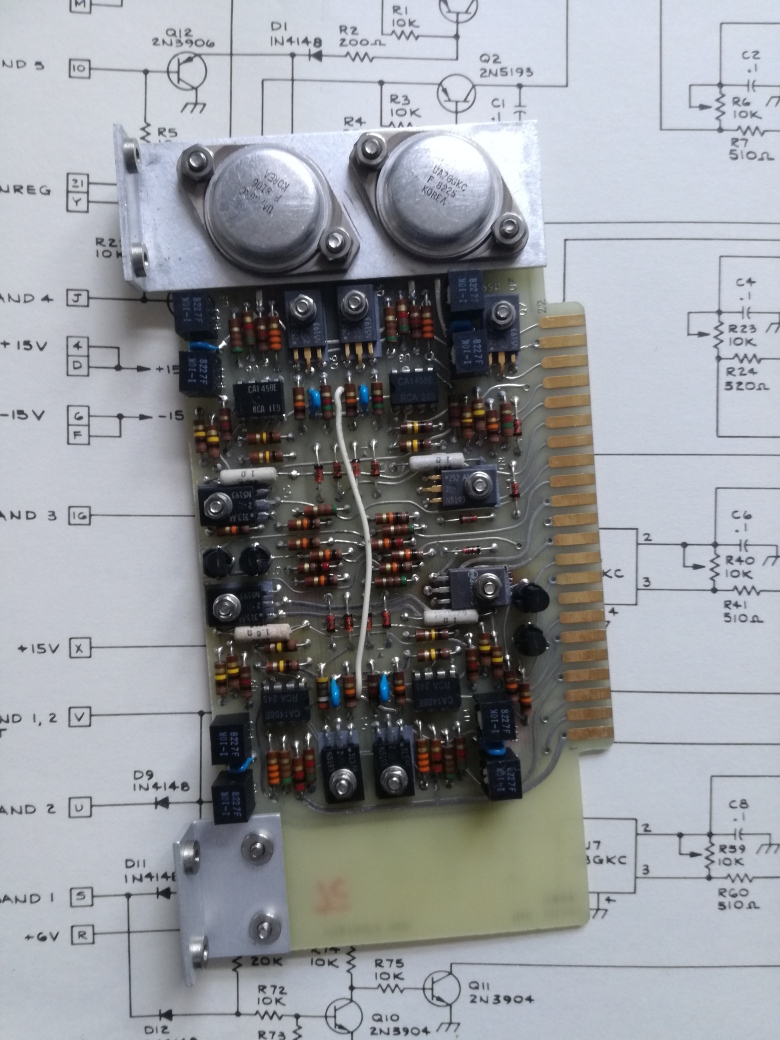

The register settings – running the Si5351A VCO at 780 MHz allows the use of integer-only dividers.

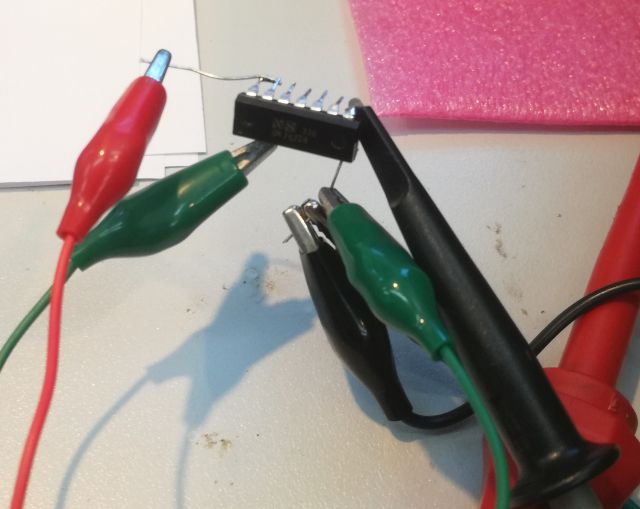

Capacitance set to 4 pF (the lowest value possible for the Si5351A, but it has little effect on sensitivity, 10 pF default setting works as well, maybe 1 dB decreased sensitivity, but we are anyway feeding more then enough power to the Xtal A input of the Si5351A).

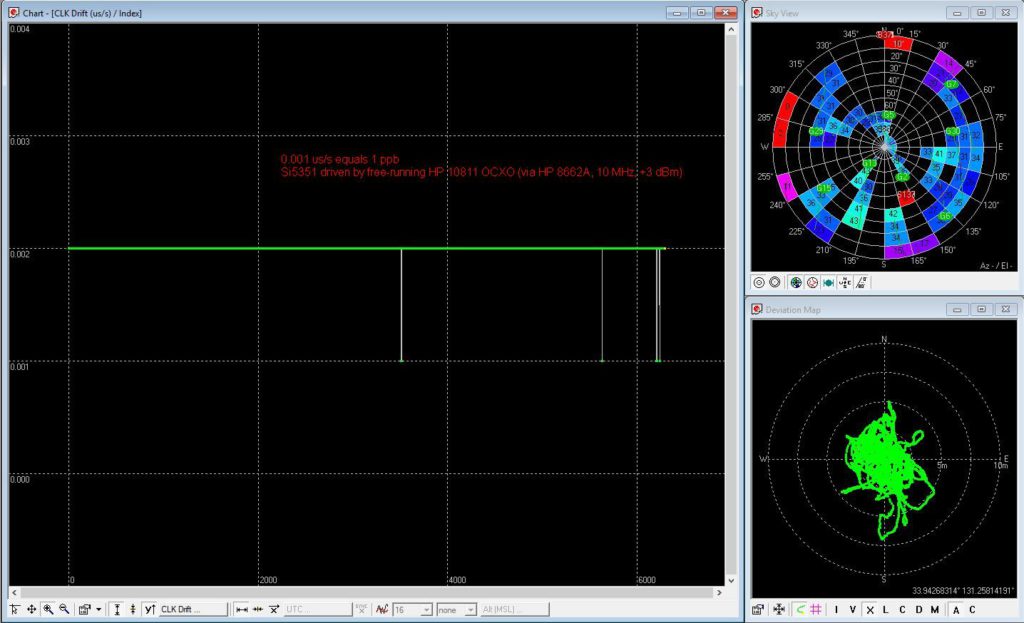

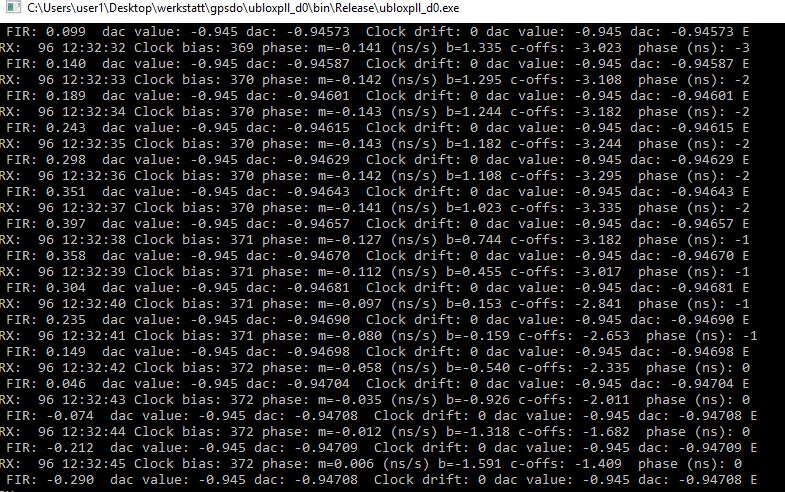

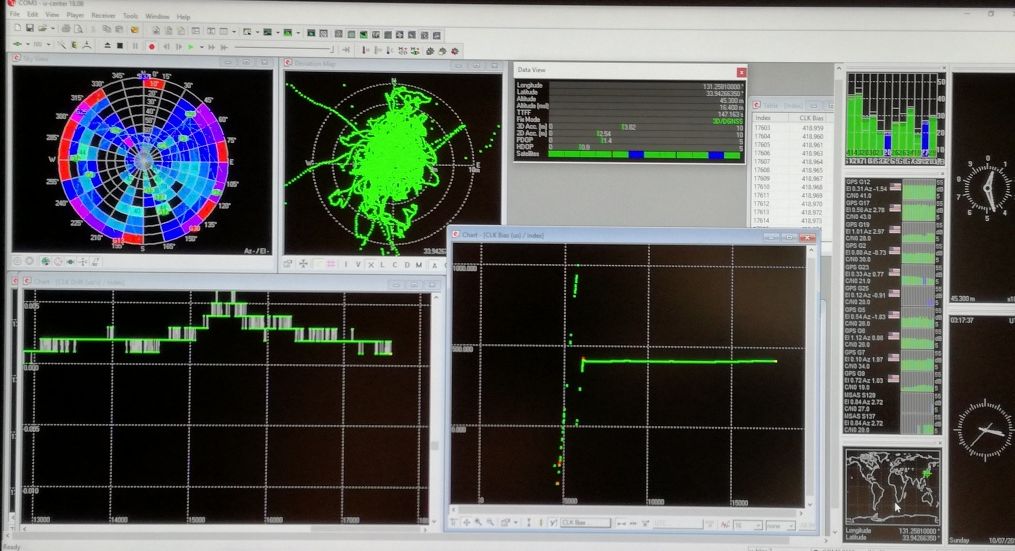

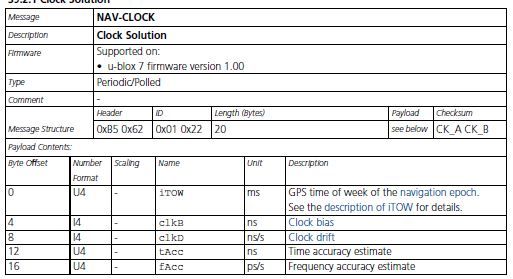

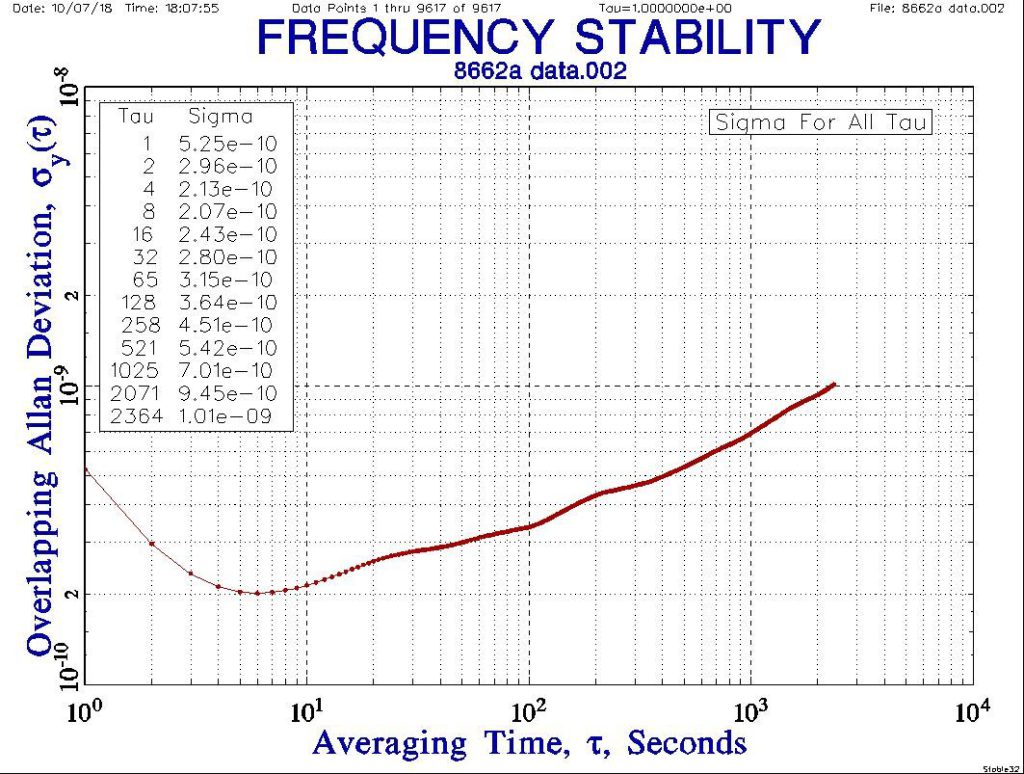

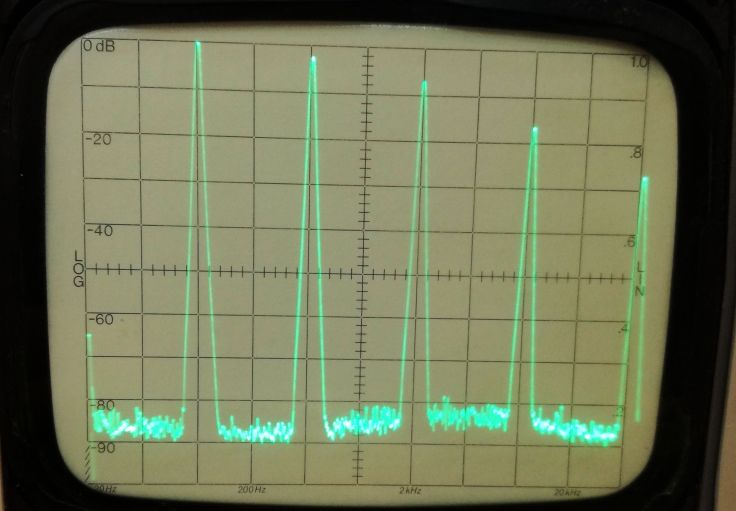

The GPS clock drift data – not very exiting – no drift at all, less than 1 ppb over a few hours. There is a slight frequency offset, because the electronic frequency control (EFC) of the 10811A OCXO set to 0 Volt, rather to the proper value for exactly 10 MHz, only for convenience and to avoid any artifacts from EFC DAC noise or drift.

The position accuracy also seems better with the stable oscillator, but may need to check this again after acquiring data for a full day or so.

All in all, more than a proof of concept. Next steps include setting up a stand-alone OCXO (I have a couple of spare 10811A OCXOs around), a distribution amplifier (nothing special, planning to use some 74HC14 with small signal transformers for isolation), and getting the PLL code into a microcontroller. For the DAC, I will use a fairly basic model, and provide a low pass filter at the output (much faster than the digitally-generated long time constant low pass of the PLL loop, but still slow compared to common standards) to reduce noise.

So far, the bill of material is very low, just a few dollars, including the GPS receiver. My goal is to stay below USD 10 total, excluding the OCXO, to achieve better than 10-9 stability, and an output with no jitter or other issues.